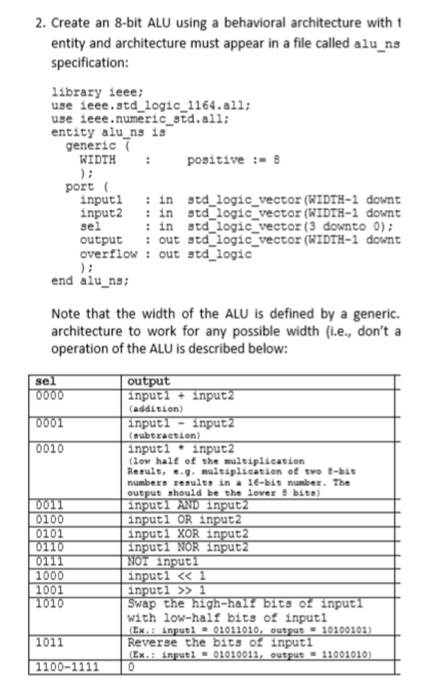

2. Create an 8-bit ALU using a behavioral architecture with 1 entity and architecture must appear in a file called aluns specification: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity alu_ns is generic positive : 3 ); port inputi in std_logic_vector (WIDTH-1 downt input2 : in std_logic_vector (WIDTH-1 downt sel in std_logic_vector (3 downto 0); output out std_logic_vector (WIDTH-1 downt overflow: out std_logic ): end alu_ns; Note that the width of the ALU is defined by a generic. architecture to work for any possible width (i.e., don't a operation of the ALU is described below: sel 0000 0001 0010 0011 0100 0101 0111 1000 1001 1010 output inpucl + inputz (addition) inputi - Input2 (subtraction) inputl input2 (low half of the multiplication Resuls, e.g. multiplication of t h is numbers results in a 16-bit number. The output should be the lover bits) Input1 AND inputz input1 OR input2 input1 XOR input2 Inputi NOR Input2 NON Input Inputi > 1 Swap the high-hal bits o inputi with low-half bits of input1 (Ex.: input1 - 01011010, output - 10100103) Reverse the bits of inputi Ex.: input1 - 01010011, output - 11001010) 1011 1100-1111 2. Create an 8-bit ALU using a behavioral architecture with 1 entity and architecture must appear in a file called aluns specification: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity alu_ns is generic positive : 3 ); port inputi in std_logic_vector (WIDTH-1 downt input2 : in std_logic_vector (WIDTH-1 downt sel in std_logic_vector (3 downto 0); output out std_logic_vector (WIDTH-1 downt overflow: out std_logic ): end alu_ns; Note that the width of the ALU is defined by a generic. architecture to work for any possible width (i.e., don't a operation of the ALU is described below: sel 0000 0001 0010 0011 0100 0101 0111 1000 1001 1010 output inpucl + inputz (addition) inputi - Input2 (subtraction) inputl input2 (low half of the multiplication Resuls, e.g. multiplication of t h is numbers results in a 16-bit number. The output should be the lover bits) Input1 AND inputz input1 OR input2 input1 XOR input2 Inputi NOR Input2 NON Input Inputi > 1 Swap the high-hal bits o inputi with low-half bits of input1 (Ex.: input1 - 01011010, output - 10100103) Reverse the bits of inputi Ex.: input1 - 01010011, output - 11001010) 1011 1100-1111