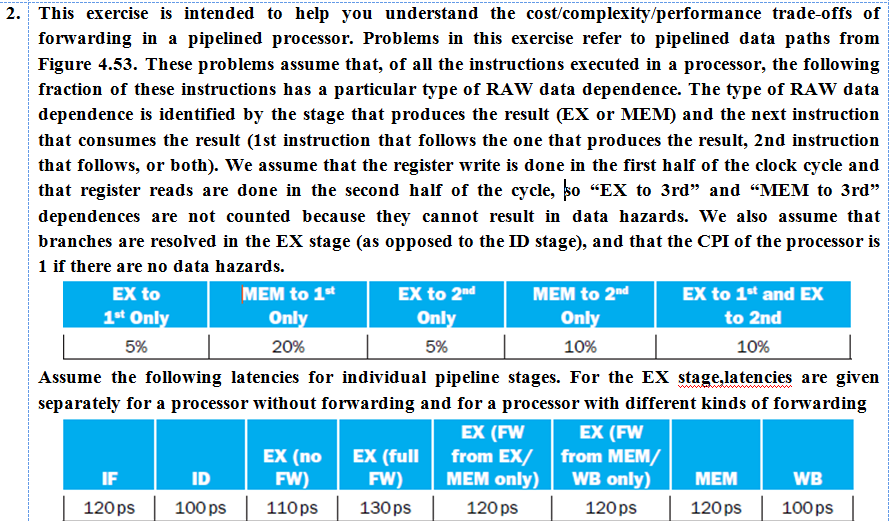

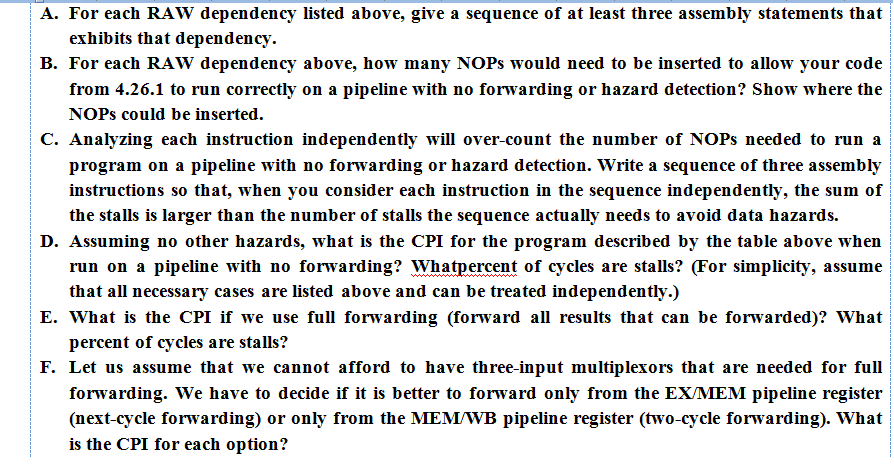

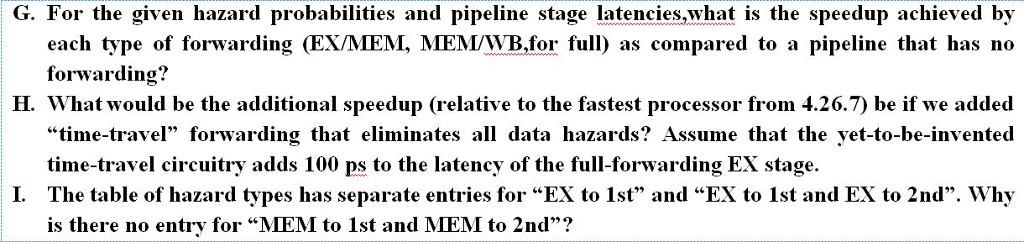

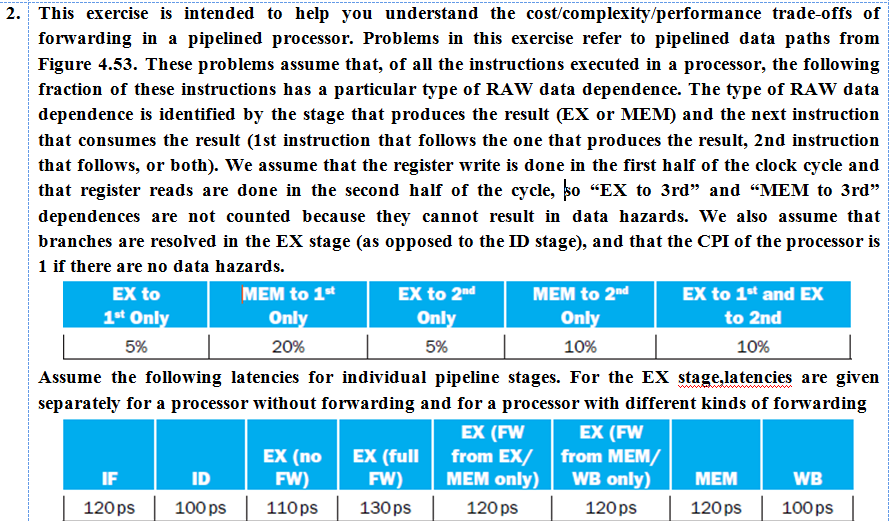

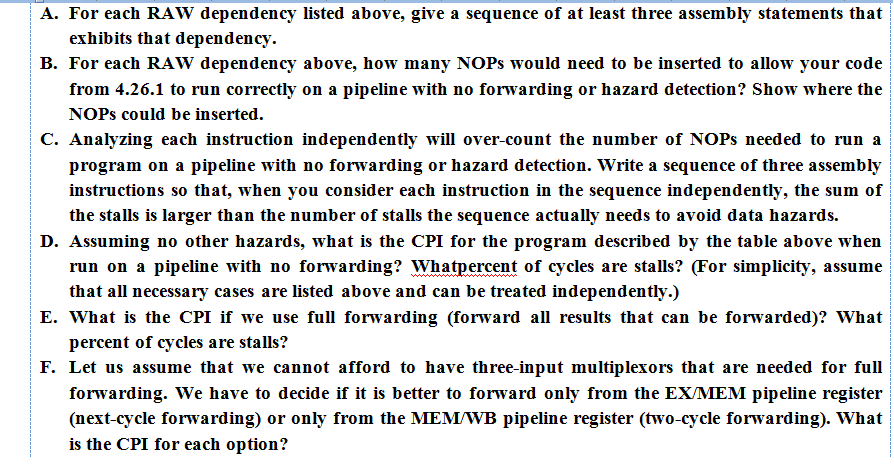

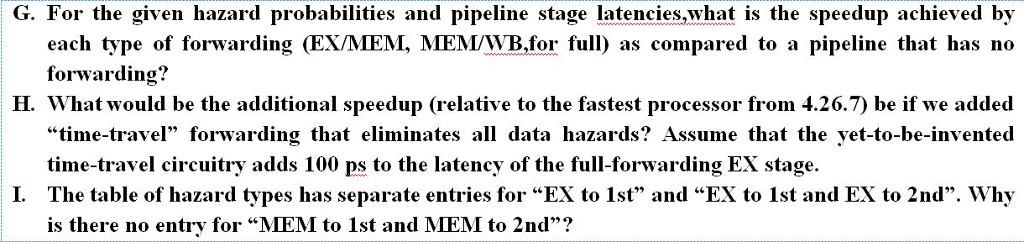

2. This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined data paths from Figure 4.53. These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions has a particular type of RAW data dependence. The type of RAW data dependence is identified by the stage that produces the result (EX or MEM) and the next instruction that consumes the result (1st instruction that follows the one that produces the result, 2nd instruction that follows, or both). We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, o EX to 3rd" and NIEM to 3rd dependences are not counted because thev cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. EX to 1st Onl 5% MEM to 1st Onl 20% EX to 2nd Onl 5% MEM to 2nd Onl 10% EX to 1st and EX to 2nd 1096 Assume the following latencies for individual pipeline stages. For the EX stage,latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding EX (FW EX (FW EX (no EX (full from EX/ from MEM/ ID FW) 110ps FW) MEM only) WB only)MEM 130 ps WB 120ps 100ps 11 120 ps 120ps 120 ps 100 ps 2. This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined data paths from Figure 4.53. These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions has a particular type of RAW data dependence. The type of RAW data dependence is identified by the stage that produces the result (EX or MEM) and the next instruction that consumes the result (1st instruction that follows the one that produces the result, 2nd instruction that follows, or both). We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, o EX to 3rd" and NIEM to 3rd dependences are not counted because thev cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. EX to 1st Onl 5% MEM to 1st Onl 20% EX to 2nd Onl 5% MEM to 2nd Onl 10% EX to 1st and EX to 2nd 1096 Assume the following latencies for individual pipeline stages. For the EX stage,latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding EX (FW EX (FW EX (no EX (full from EX/ from MEM/ ID FW) 110ps FW) MEM only) WB only)MEM 130 ps WB 120ps 100ps 11 120 ps 120ps 120 ps 100 ps