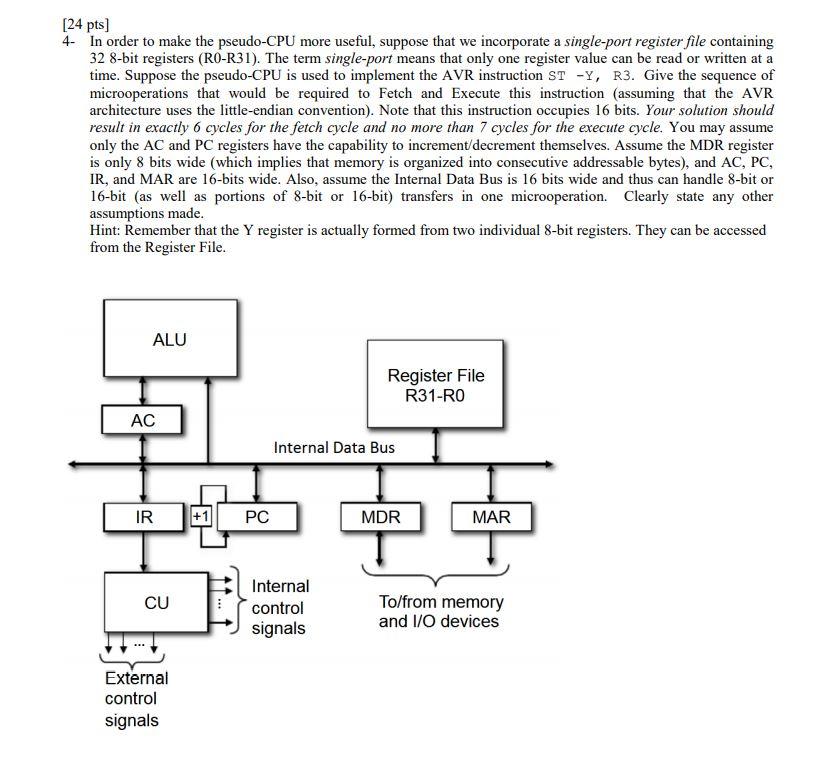

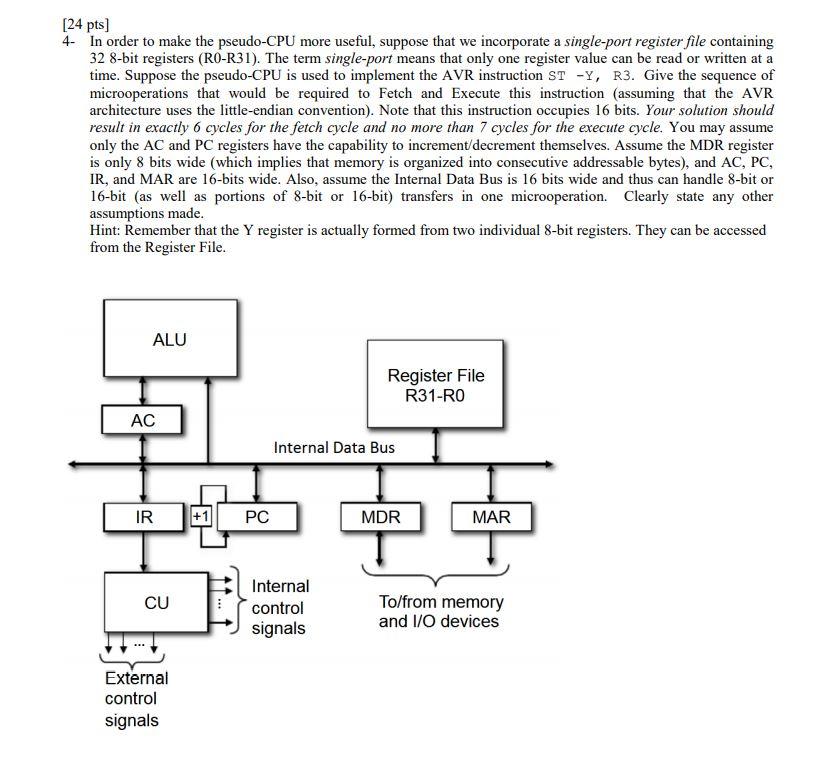

[24 pts) 4- In order to make the pseudo-CPU more useful, suppose that we incorporate a single-port register file containing 32 8-bit registers (RO-R31). The term single-port means that only one register value can be read or written at a time. Suppose the pseudo-CPU is used to implement the AVR instruction ST -Y, R3. Give the sequence of microoperations that would be required to Fetch and Execute this instruction (assuming that the AVR architecture uses the little-endian convention). Note that this instruction occupies 16 bits. Your solution should result in exactly 6 cycles for the fetch cycle and no more than 7 cycles for the execute cycle. You may assume only the AC and PC registers have the capability to increment/decrement themselves. Assume the MDR register is only 8 bits wide (which implies that memory is organized into consecutive addressable bytes), and AC, PC, IR, and MAR are 16-bits wide. Also, assume the Internal Data Bus is 16 bits wide and thus can handle 8-bit or 16-bit (as well as portions of 8-bit or 16-bit) transfers in one microoperation. Clearly state any other assumptions made. Hint: Remember that the Y register is actually formed from two individual 8-bit registers. They can be accessed from the Register File. ALU Register File R31-RO AC Internal Data Bus IR +1 PC MDR MAR CU Internal control signals To/from memory and I/O devices External control signals [24 pts) 4- In order to make the pseudo-CPU more useful, suppose that we incorporate a single-port register file containing 32 8-bit registers (RO-R31). The term single-port means that only one register value can be read or written at a time. Suppose the pseudo-CPU is used to implement the AVR instruction ST -Y, R3. Give the sequence of microoperations that would be required to Fetch and Execute this instruction (assuming that the AVR architecture uses the little-endian convention). Note that this instruction occupies 16 bits. Your solution should result in exactly 6 cycles for the fetch cycle and no more than 7 cycles for the execute cycle. You may assume only the AC and PC registers have the capability to increment/decrement themselves. Assume the MDR register is only 8 bits wide (which implies that memory is organized into consecutive addressable bytes), and AC, PC, IR, and MAR are 16-bits wide. Also, assume the Internal Data Bus is 16 bits wide and thus can handle 8-bit or 16-bit (as well as portions of 8-bit or 16-bit) transfers in one microoperation. Clearly state any other assumptions made. Hint: Remember that the Y register is actually formed from two individual 8-bit registers. They can be accessed from the Register File. ALU Register File R31-RO AC Internal Data Bus IR +1 PC MDR MAR CU Internal control signals To/from memory and I/O devices External control signals