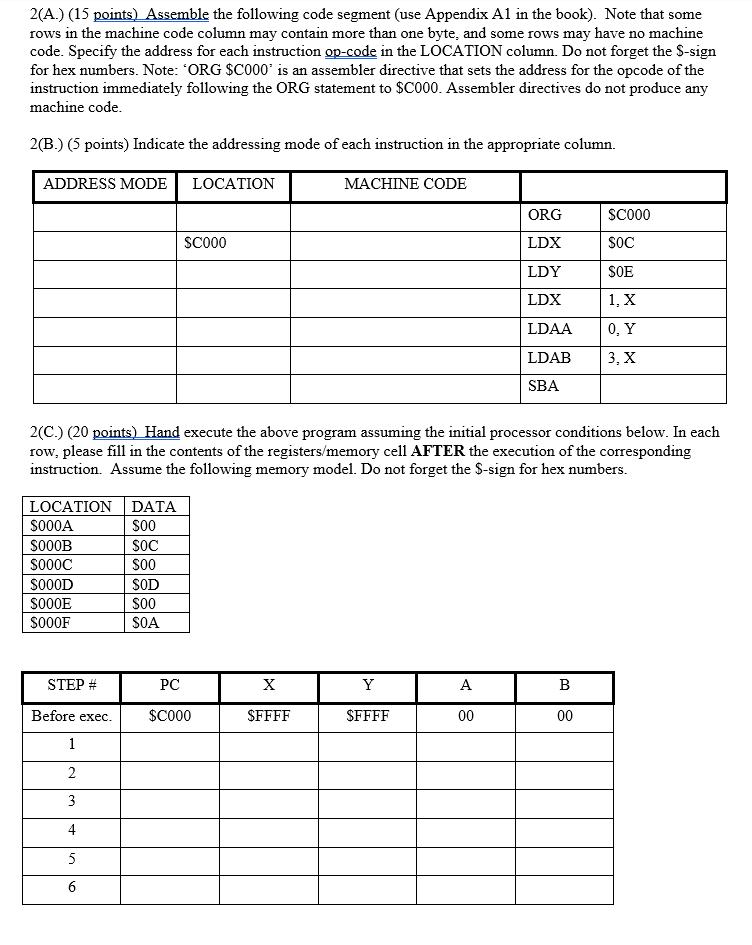

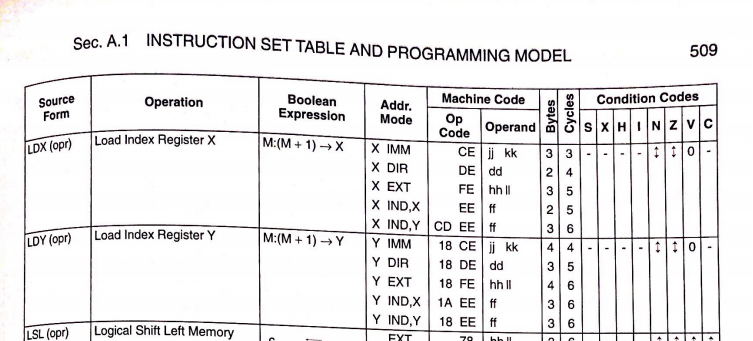

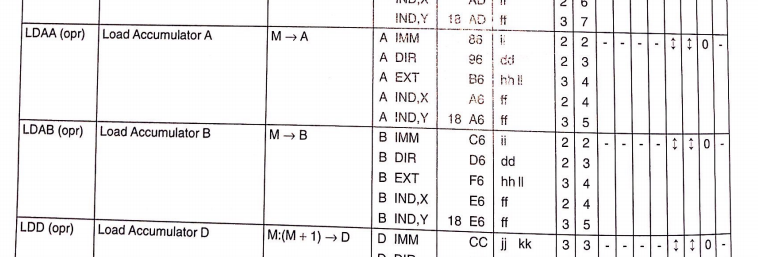

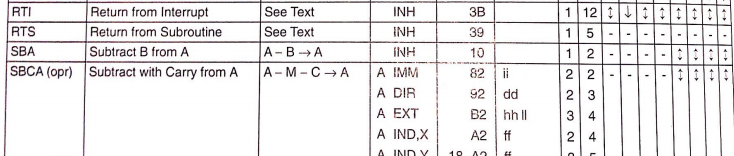

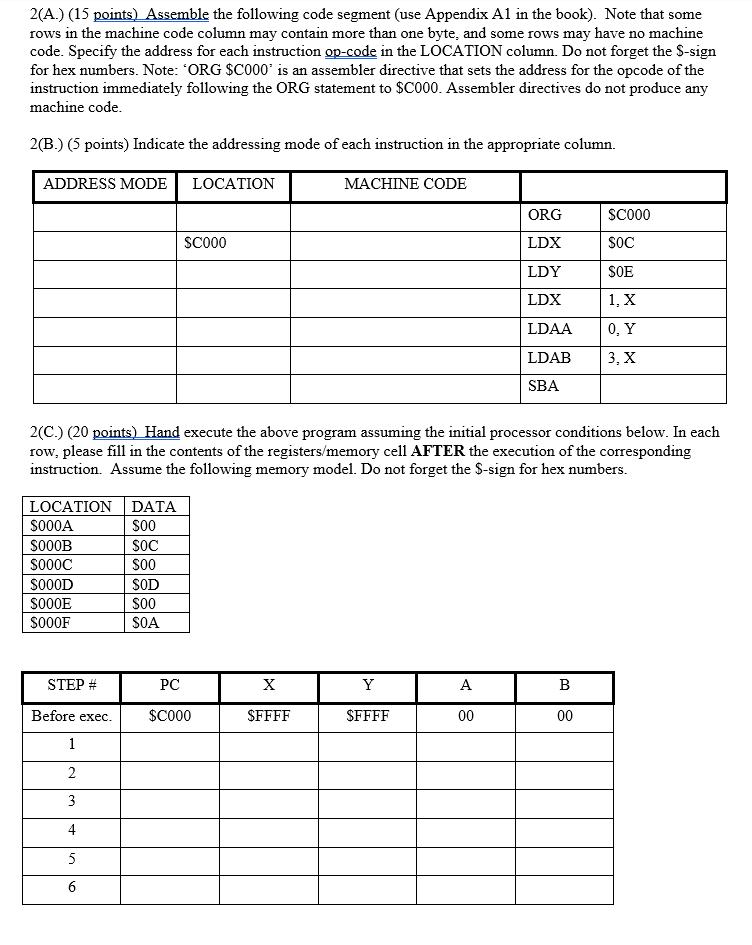

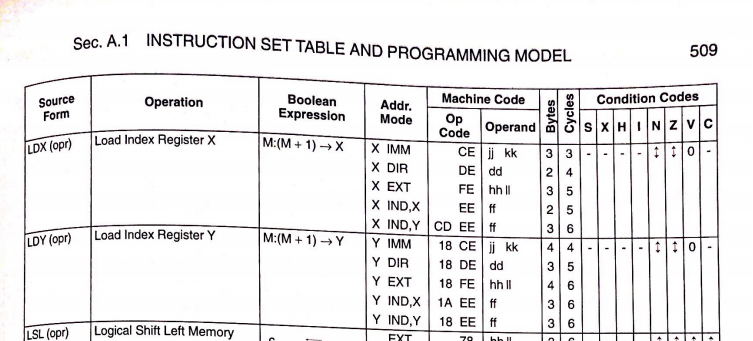

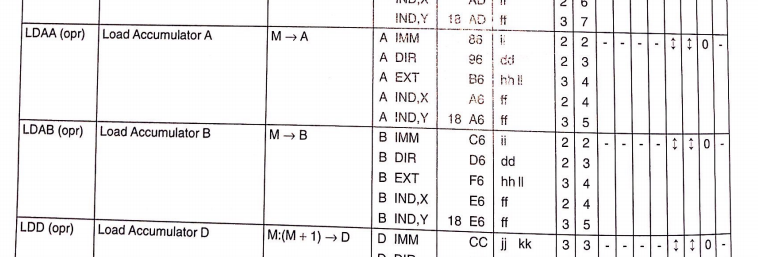

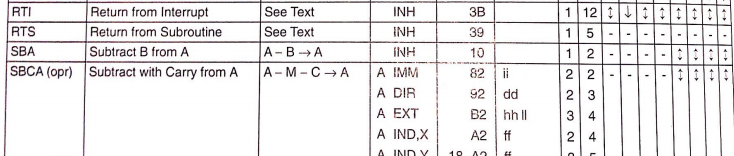

2(A.) (15 points) Assemble the following code segment (use Appendix A1 in the book). Note that some rows in the machine code column may contain more than one byte, and some rows may have no machine code. Specify the address for each instruction op-code in the LOCATION column. Do not forget the S-sign for hex numbers. Note: 'ORG $C000' is an assembler directive that sets the address for the opcode of the instruction immediately following the ORG statement to $C000. Assembler directives do not produce any machine code. 2(B.) (5 points) Indicate the addressing mode of each instruction in the appropriate column. | ADDRESS MODE LOCATION MACHINE CODE SC000 ORG SC000 LDX SOC LDY SOE LDX1, X LDAA 0,Y LDAB 3, X SBA 2(C.) (20 points) Hand execute the above program assuming the initial processor conditions below. In each row, please fill in the contents of the registers/memory cell AFTER the execution of the corresponding instruction. Assume the following memory model. Do not forget the $-sign for hex numbers. LOCATION DATA SOO0A SOO SOOOB SOC SOOOC S00 SOOOD SOD SOO0E S00 SOOOF SOA STEP # Before exec. PCX $C000 Y $FFFF 00 00 SFFFF L Sec. A.1 INSTRUCTION SET TABLE AND PROGRAMMING MODEL 509 Source Operation Condition Codes Boolean Expression Addr. Mode Machine Code Op Form Code Operand px (opr) Load Index Register X ol M:(M+ 1) X CE -- - 1 DE WWWWNWNW Bytes OOOO A OU AW Cycles ny (opr) Load Index Register Y M:(M +1) X IMM ikk X DIR dd X EXT FE hh II X IND,X X INDY CD EE Y IMM 18 CE jjkk Y DIR 18 DE Y EXT 18 FE hh ! Y IND, X 1A EEff Y IND.Y 18 EEff FYT 1 Y LSL (opr) Logical Shift Left Memory zobu 18 AD LDAA (opr) Load Accumulator A MA - - - B6 INDY A IMM A DIR A EXT A IND, X A IND,Y B IMM B DIR B EXT B INDEX BIND, Y 18 A6 ff LDAB (opr) Load Accumulator B M B D6 F6 E6 18 E6 CC hh II ff ff kk LDD (opr) Load Accumulator D M:(M+1) 33-1---1110:1 INH 15 -- RTI RTS SBA SBCA (opr) Return from Interrupt Return from Subroutine Subtract B from A Subtract with Carry from A See Text See Text A-BA A-M-C - A ---111111 INH INH A MM A DIR A EXT A IND,X A ININ Y 10 A 2(A.) (15 points) Assemble the following code segment (use Appendix A1 in the book). Note that some rows in the machine code column may contain more than one byte, and some rows may have no machine code. Specify the address for each instruction op-code in the LOCATION column. Do not forget the S-sign for hex numbers. Note: 'ORG $C000' is an assembler directive that sets the address for the opcode of the instruction immediately following the ORG statement to $C000. Assembler directives do not produce any machine code. 2(B.) (5 points) Indicate the addressing mode of each instruction in the appropriate column. | ADDRESS MODE LOCATION MACHINE CODE SC000 ORG SC000 LDX SOC LDY SOE LDX1, X LDAA 0,Y LDAB 3, X SBA 2(C.) (20 points) Hand execute the above program assuming the initial processor conditions below. In each row, please fill in the contents of the registers/memory cell AFTER the execution of the corresponding instruction. Assume the following memory model. Do not forget the $-sign for hex numbers. LOCATION DATA SOO0A SOO SOOOB SOC SOOOC S00 SOOOD SOD SOO0E S00 SOOOF SOA STEP # Before exec. PCX $C000 Y $FFFF 00 00 SFFFF L Sec. A.1 INSTRUCTION SET TABLE AND PROGRAMMING MODEL 509 Source Operation Condition Codes Boolean Expression Addr. Mode Machine Code Op Form Code Operand px (opr) Load Index Register X ol M:(M+ 1) X CE -- - 1 DE WWWWNWNW Bytes OOOO A OU AW Cycles ny (opr) Load Index Register Y M:(M +1) X IMM ikk X DIR dd X EXT FE hh II X IND,X X INDY CD EE Y IMM 18 CE jjkk Y DIR 18 DE Y EXT 18 FE hh ! Y IND, X 1A EEff Y IND.Y 18 EEff FYT 1 Y LSL (opr) Logical Shift Left Memory zobu 18 AD LDAA (opr) Load Accumulator A MA - - - B6 INDY A IMM A DIR A EXT A IND, X A IND,Y B IMM B DIR B EXT B INDEX BIND, Y 18 A6 ff LDAB (opr) Load Accumulator B M B D6 F6 E6 18 E6 CC hh II ff ff kk LDD (opr) Load Accumulator D M:(M+1) 33-1---1110:1 INH 15 -- RTI RTS SBA SBCA (opr) Return from Interrupt Return from Subroutine Subtract B from A Subtract with Carry from A See Text See Text A-BA A-M-C - A ---111111 INH INH A MM A DIR A EXT A IND,X A ININ Y 10 A