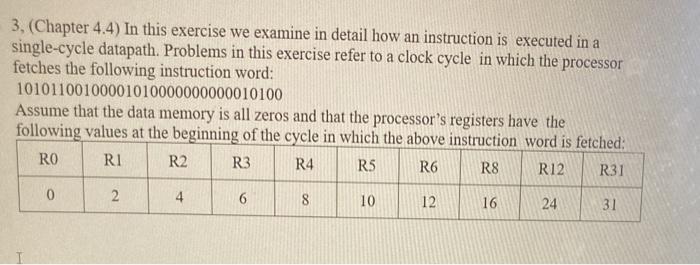

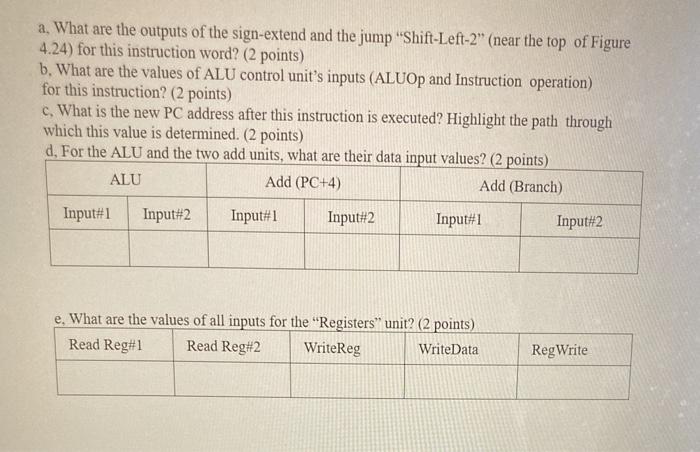

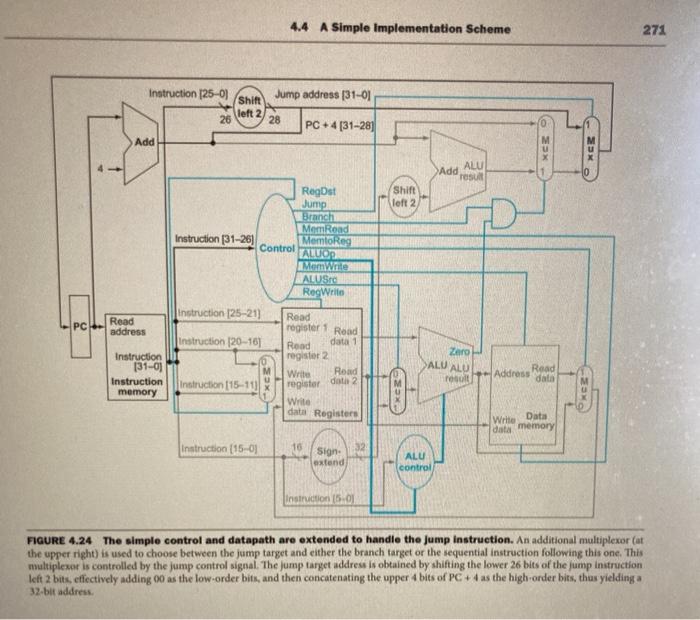

3, (Chapter 4.4) In this exercise we examine in detail how an instruction is executed in a single-cycle datapath. Problems in this exercise refer to a clock cycle in which the processor fetches the following instruction word: 10101100100001010000000000010100 Assume that the data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which the above instruction word is fetched: RO RI R2 R3 R4 R5 R6 R12 R31 R8 0 2 4 6 8 10 12 16 24 31 a. What are the outputs of the sign-extend and the jump "Shift-Left-2" (near the top of Figure 4.24) for this instruction word? (2 points) b. What are the values of ALU control unit's inputs (ALUOp and Instruction operation) for this instruction? (2 points) c. What is the new PC address after this instruction is executed? Highlight the path through which this value is determined. (2 points) d. For the ALU and the two add units, what are their data input values? (2 points) ALU Add (PC+4) Add (Branch) Input#1 Input#2 Input#1 Input#2 Input#1 Input#2 e. What are the values of all inputs for the "Registers" unit? (2 points) Read Reg#1 Read Reg#2 WriteReg WriteData Reg Write 4.4 A Simple Implementation Scheme 271 Instruction (25-01 Shift Jump address (31-01 26 left 2 28 PC +4 [31-28) Add EX Add ALU resu Shift loft 2 Regst Jump Branch MemRond Instruction (31-26) MomtoReg Control TALUOD MomWrite ALUSTO RogWrite instruction 125-21 Read register 1 Road Instruction (20-161 data 1 Road register 2 Write Road Instruction (15-11) register doti 2 Write data Register PC Read address Zero ALU ALU Instruction (31-01 Instruction memory Read xea Address to ret xez Write Data ta memory Instruction (15-01 10 Sign:32 extend ALU control Instruction 15.00 FIGURE 4.24 The simple control and datapath are extended to handle the Jump instruction. An additional multiplexor (at the upper right) is used to choose between the jump target and either the branch target or the sequential instruction following this one. This multiplexer is controlled by the jump control signal. The jump target address is obtained by shifting the lower 26 bits of the jump Instruction left 2 bits, effectively adding 00 as the low-order bits, and then concatenating the upper 4 bits of PC + 4 as the high-order bits, thus yielding a 32-bit address