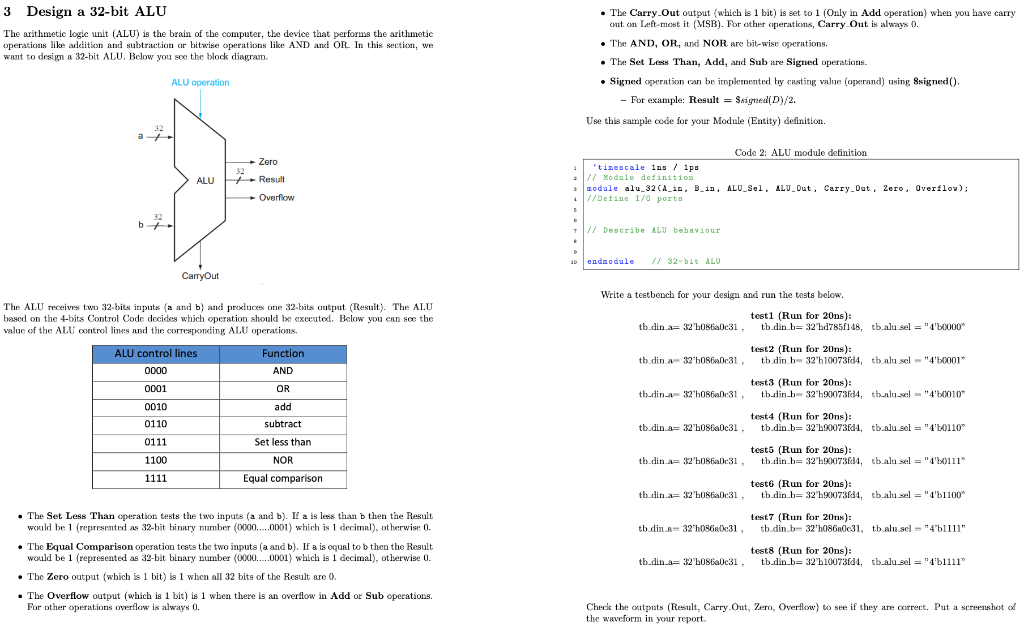

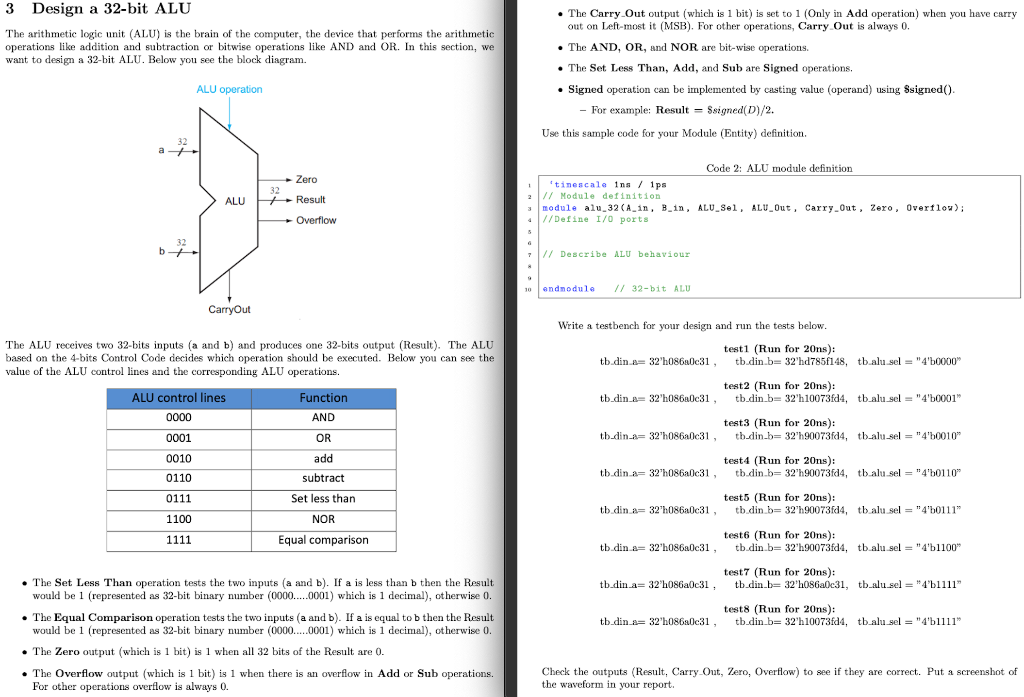

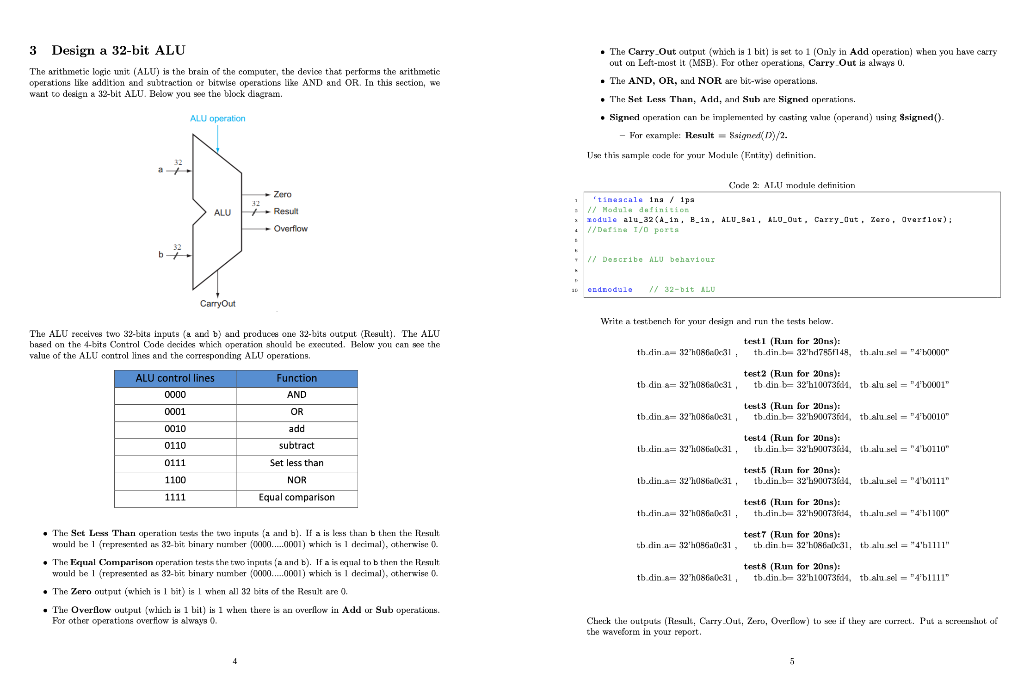

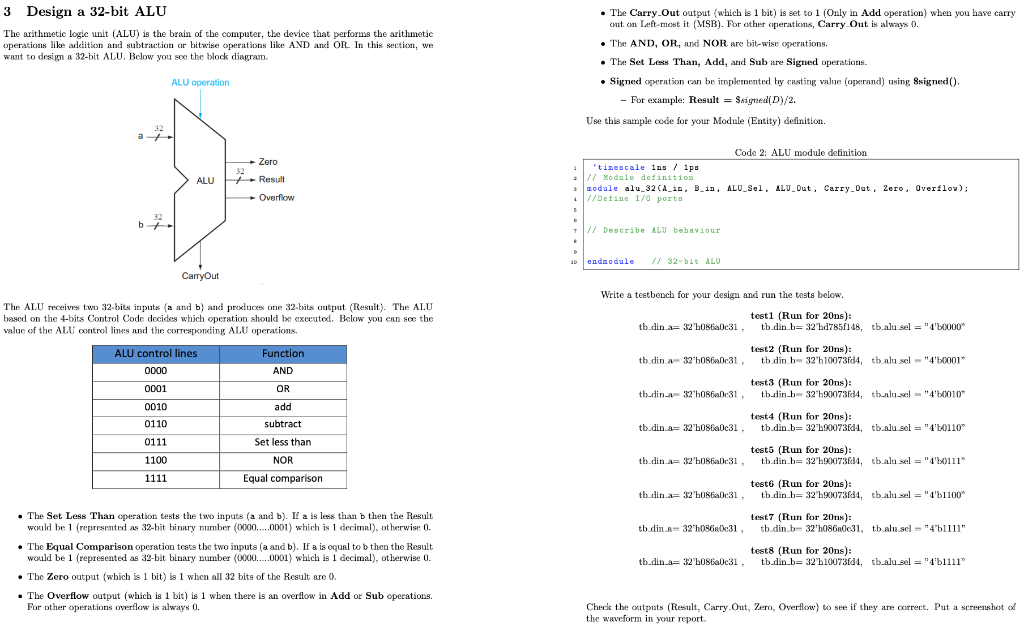

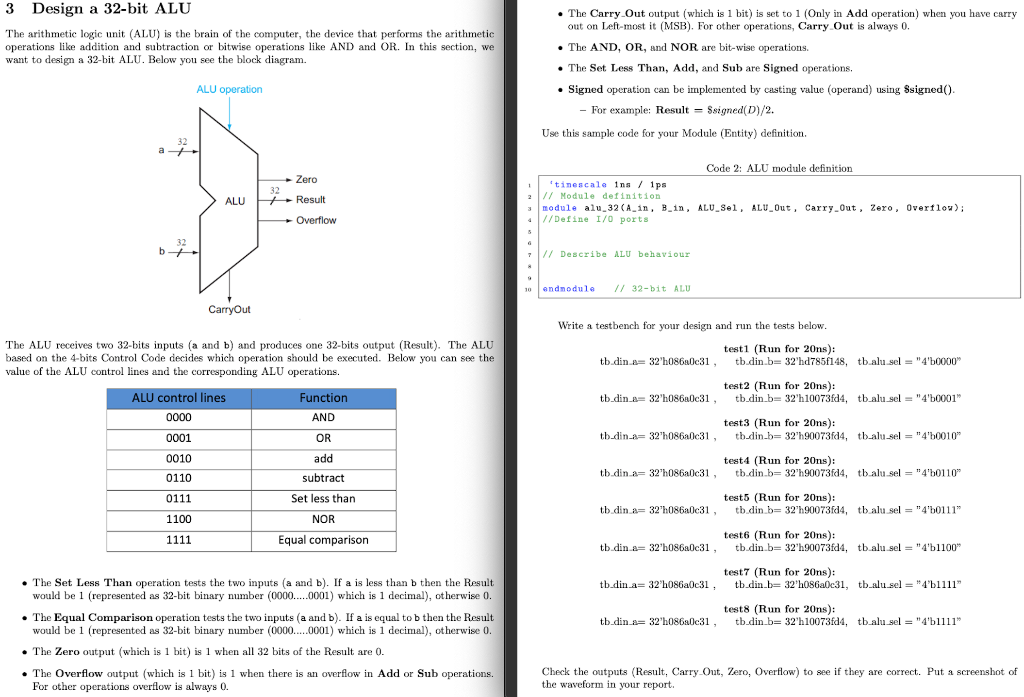

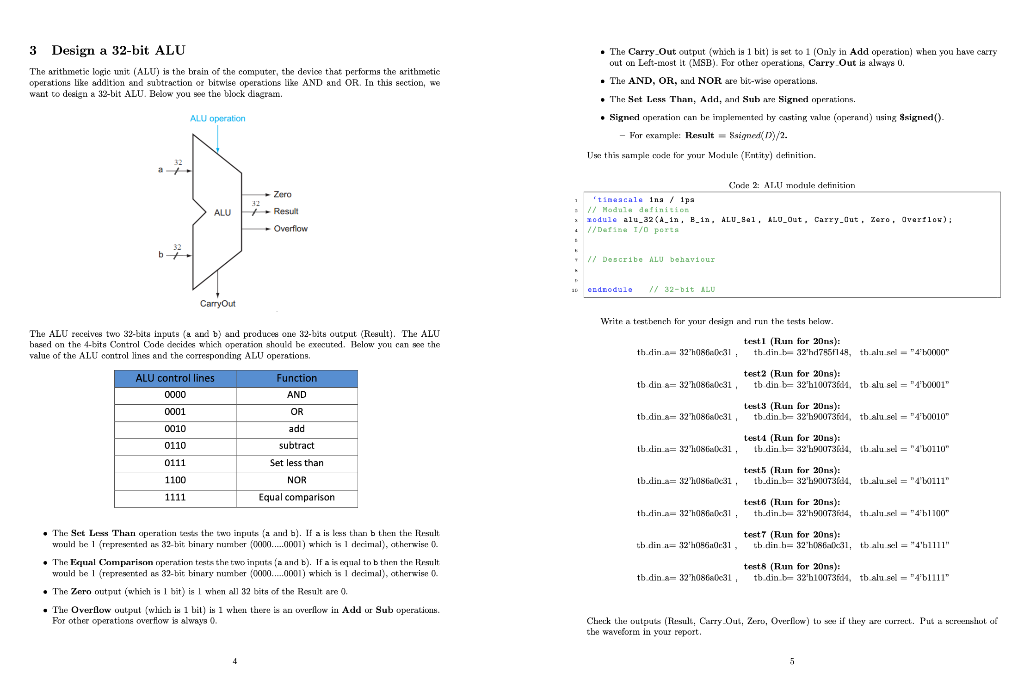

3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most it (MSB). For other operations, Carry Out is always 0. The AND, OR, ani NOR are bit-wise operations, The Set Less Than, Add, and Sub are Signed operations. Signed cymeration can be impkemented by casting value operand) using Ssigned(). - For example: Result = SaignedD)/2. Use this sample code for your Module (Entity) definition. ALU operation Zero 32 Code 2: ALU module definition / // Module definition > module alu_32 (4_1n, B.in, ALU_Sel, ALU_Out, Carry Out, Zero, Overflow); // Define I/O ports ALU Result Overflow b + T // Describe ALU behaviour a ondmodule // 32-bit ALU CarryOut Write a testbench for your design and run the tests below. The ALU receives two 32-bits inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations. tb.dina 32'b08ba0c31, test 1 (Run for 20ns): tb din.b=32 hd785f148, tb alu sel = "1'00000 ALU control lines 0000 Function AND tb din 32'hostaDc31, test2 (Run for 20ns): tb din b-32"h10073fd4, tb alusel-"410001 0001 OR tbudin32'h086ac31 test3 (Run for 20ns): tbulin-b-32"-90073fd4, thualusel - "410010 add 0010 0110 tb.din.a32'LO8ba0c31 test 4 (Run for 20ns): tb din.b=32 690073fd4, tb alusel = "4'10110 0111 subtract Set less than NOR Equal comparison 1100 tb din a=32"hostaDc31, test5 (Run for 20ns): tb.din b=32'h90073fd4, tb alusel = "4'10111" 1111 test (Run for 20ns): tb. din.b=32'h90073fd4, tb alusel = "4'1100 tb din 32'hostaDc31, test 7 (Run for 20ns): tb din.b=32'h0860c31, tb alusel = 4b1111" tb din s=32"h09680c31, The Set Less Than operation test the two inputs (a and b). If a is less than then the Result would be 1 (represented as 32-bit binary number (0000.....0001) which is 1 decimal), otherwise 0. The Equal Comparison operation test the two inputs (a and b). If a is equal to b then the Result would be 1 (represented as 32-bit binary number (0000...0001) which is 1 decimal), otherwise 0. The Zero output (which is 1 bit) is 1 when all 32 bits of the Result are 0. The Overflow output (which is 1 bit) is 1 when there is an overflow in Add or Sub operations. For other operations overflow is always 0. tb.din.a=32'hosta0c31, test8 (Run for 20ns): tb din b=32 h10073fd1, tbalu sel = "{'b1111 Check the outputs (Result, Carry Out, Zero, Overflow) to see if they are correct. Put a screenshot of the waveform in your report 3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most it (MSB). For other operations, Carry Out is always 0. The AND, OR, and NOR are bit-wise operations, The Set Less Than, Add, and Sub are Signed operations, Signed operation can be implemented by casting value (operand) using Ssigned(). - For example: Result = $signed(D)/2. Use this sample code for your Module (Entity) definition, ALU operation 32 1 ALU Zero 32 7 Result Overflow Code 2: ALU module definition tinescale ins / 1ps 21 Module definition module alu_32 (A_in, B.in, ALU_Sel, ALU_Out, Carry-Out, Zero, Overflow); // Define I/O ports 5 0 32 b+ 7 // Describe ALU behaviour 9 10 andmodule // 32-bit ALU CarryOut The ALU receives two 32-bits inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations. Write a testbench for your design and run the tests below. testi (Run for 20ns): tb din = 32'h086a0c31, tb.din.b= 32"hd785f148, tb alu.sel = "4"00000 test2 (Run for 20ns): tb din a=32'h086a0c31 tb din b=32'h10073fd4, tb alu sel = "4'60001" ALU control lines Function AND 0000 test 3 (Run for 20ns): th_din_b=32"h90073fd4, tb alusel = "4'50010" 0001 OR tb.din.s=32'h086a0c31, 0010 add tb.din.a- 32'h086a6c31 test 4 (Run for 20ns): tb din b=32"h90073fd4, tb alu sel = "4'10110" 0110 subtract 0111 Set less than tb din a=32'h08690031 1100 NOR test5 (Run for 20ns): tb din b=32"h90073fd4, tb alu.sel = "4'10111" test6 (Run for 20ns): tb din.b=32'h90073fd4, tb alu sel = "4b1100" 1111 Equal comparison tb din a=32'h086a0c31 , test 7 (Run for 20ns): tb.din.a= 32 h086a0c31, tb din.b=32'4086a6c31, tb_alu sel = "4"b1111" test8 (Run for 20ns): tb din a= 32'h086a0c31, tb_din_b= 32'h10073fd4, tb_alu sel = "4b1111" The Set Less Than operation tests the two inputs (a and b). If a is less than b then the Result would be 1 (represented as 32-bit binary number (0000....0001) which is 1 decimal), otherwise 0. The Equal Comparison operation tests the two inputs (a and b). If a is equal to b then the Result would be 1 (represented as 32-bit binary number (0000.....0001) which is 1 decimal), otherwise 0. The Zero output (which is 1 bit) is 1 when all 32 bits of the Result are 0. The Overflow output (which is 1 bit) is 1 when there is an overflow in Add Sub operations. For other operations overflow is always 0. Check the outputs (Result, Carry Out, Zero, Overflow) to see if they are correct. Put a screenshot of the waveform in your report. 3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most It (MSB). For other operations. Carry Out is always 0. The AND, OR, and NOR are bit-wise operations. The Set Less Than, Add, and Sub are signed operations. Signed operation can be implemented by casting value (operand) using Ssigned(). - For example: Result = Signe Dy/2. Use this simple code for your Module (Entity) detinition. ALU operation -Zero 32 Code 2: ALU module definition 1 'tinescale ina / ipa // Module definition > Iodule alu_32 (A_1n, B_1n, ALU_Se1, ALU_Out. Carry-out, Zero, Overflow): //Dafina T/O Ports ALU - Overflow bH Describe ALU behaviour cudnodulo // 32-bit ALU CarryOut Write a testbench for your design and run the tests below. th dina 32"h08fa31 test I (Run for 20ns): th din.b32"hd755F149, th alusel = "4501000" The ALU receives two 32-bita inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations, ALU control lines Function 0000 AND tb din a=32 h086a1c31 test2 (Run for 20ns): tb din b=32'b10073fd1, tb alu sel = "110001" 0001 OR add tb din A-32'h08680c31 Lest3 (Run for 20ns): tb dint=32'590073fd4, tb alusel = "450010" 0010 0110 subtract tb diu a=32 1.08ba31 test 4 (Run for 20ns): tb din bs=32690073fd4, tb alu.se = "4'0110" 0111 1100 Set less than NOR tb dius=32 til 31, test 5 (Run for 20ns): tb diu_b=32'59007364, tb alusel = "4'10111" 1111 Equal comparison th_din.A 32"h08fa31 , test 6 (Run for 20ns): th_din. 32'0007344, thalusel "1100" tb din it=320661031, test 7 (Run for 20ns): tb din b=32'h0basi, tb alusel "4b1111" The Sct Less Than operation tests the two inputs (a and b). If a is less than b then the Result would he 1 (represented as 32-bit binary number (0000......0001) which is 1 decimal), cotherwise 0. The Equal Comparison operation tests the two inputs (a and b). If a isual to be then the Result would be 1 (represented as 32-bit binary number (0000....0001) which is i decimal), otherwise 0 The Zero output (which is 1 bit) is I when all 32 bits of the Result are O. The Overflow output (wlich is 1 bil) in 1 when there is an overflow in Add ur Sub operatius. For other operations overflow is always 0. test (Run for 20ns): tb din b-32'610073fd4, tb alusel "4'11" tb din a-32"h086131 Check the outputs (Result. Carry-Out, Zero, Overflow) to see if they are correct. Put a screen of the waveform in your report 4 5 3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most it (MSB). For other operations, Carry Out is always 0. The AND, OR, ani NOR are bit-wise operations, The Set Less Than, Add, and Sub are Signed operations. Signed cymeration can be impkemented by casting value operand) using Ssigned(). - For example: Result = SaignedD)/2. Use this sample code for your Module (Entity) definition. ALU operation Zero 32 Code 2: ALU module definition / // Module definition > module alu_32 (4_1n, B.in, ALU_Sel, ALU_Out, Carry Out, Zero, Overflow); // Define I/O ports ALU Result Overflow b + T // Describe ALU behaviour a ondmodule // 32-bit ALU CarryOut Write a testbench for your design and run the tests below. The ALU receives two 32-bits inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations. tb.dina 32'b08ba0c31, test 1 (Run for 20ns): tb din.b=32 hd785f148, tb alu sel = "1'00000 ALU control lines 0000 Function AND tb din 32'hostaDc31, test2 (Run for 20ns): tb din b-32"h10073fd4, tb alusel-"410001 0001 OR tbudin32'h086ac31 test3 (Run for 20ns): tbulin-b-32"-90073fd4, thualusel - "410010 add 0010 0110 tb.din.a32'LO8ba0c31 test 4 (Run for 20ns): tb din.b=32 690073fd4, tb alusel = "4'10110 0111 subtract Set less than NOR Equal comparison 1100 tb din a=32"hostaDc31, test5 (Run for 20ns): tb.din b=32'h90073fd4, tb alusel = "4'10111" 1111 test (Run for 20ns): tb. din.b=32'h90073fd4, tb alusel = "4'1100 tb din 32'hostaDc31, test 7 (Run for 20ns): tb din.b=32'h0860c31, tb alusel = 4b1111" tb din s=32"h09680c31, The Set Less Than operation test the two inputs (a and b). If a is less than then the Result would be 1 (represented as 32-bit binary number (0000.....0001) which is 1 decimal), otherwise 0. The Equal Comparison operation test the two inputs (a and b). If a is equal to b then the Result would be 1 (represented as 32-bit binary number (0000...0001) which is 1 decimal), otherwise 0. The Zero output (which is 1 bit) is 1 when all 32 bits of the Result are 0. The Overflow output (which is 1 bit) is 1 when there is an overflow in Add or Sub operations. For other operations overflow is always 0. tb.din.a=32'hosta0c31, test8 (Run for 20ns): tb din b=32 h10073fd1, tbalu sel = "{'b1111 Check the outputs (Result, Carry Out, Zero, Overflow) to see if they are correct. Put a screenshot of the waveform in your report 3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most it (MSB). For other operations, Carry Out is always 0. The AND, OR, and NOR are bit-wise operations, The Set Less Than, Add, and Sub are Signed operations, Signed operation can be implemented by casting value (operand) using Ssigned(). - For example: Result = $signed(D)/2. Use this sample code for your Module (Entity) definition, ALU operation 32 1 ALU Zero 32 7 Result Overflow Code 2: ALU module definition tinescale ins / 1ps 21 Module definition module alu_32 (A_in, B.in, ALU_Sel, ALU_Out, Carry-Out, Zero, Overflow); // Define I/O ports 5 0 32 b+ 7 // Describe ALU behaviour 9 10 andmodule // 32-bit ALU CarryOut The ALU receives two 32-bits inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations. Write a testbench for your design and run the tests below. testi (Run for 20ns): tb din = 32'h086a0c31, tb.din.b= 32"hd785f148, tb alu.sel = "4"00000 test2 (Run for 20ns): tb din a=32'h086a0c31 tb din b=32'h10073fd4, tb alu sel = "4'60001" ALU control lines Function AND 0000 test 3 (Run for 20ns): th_din_b=32"h90073fd4, tb alusel = "4'50010" 0001 OR tb.din.s=32'h086a0c31, 0010 add tb.din.a- 32'h086a6c31 test 4 (Run for 20ns): tb din b=32"h90073fd4, tb alu sel = "4'10110" 0110 subtract 0111 Set less than tb din a=32'h08690031 1100 NOR test5 (Run for 20ns): tb din b=32"h90073fd4, tb alu.sel = "4'10111" test6 (Run for 20ns): tb din.b=32'h90073fd4, tb alu sel = "4b1100" 1111 Equal comparison tb din a=32'h086a0c31 , test 7 (Run for 20ns): tb.din.a= 32 h086a0c31, tb din.b=32'4086a6c31, tb_alu sel = "4"b1111" test8 (Run for 20ns): tb din a= 32'h086a0c31, tb_din_b= 32'h10073fd4, tb_alu sel = "4b1111" The Set Less Than operation tests the two inputs (a and b). If a is less than b then the Result would be 1 (represented as 32-bit binary number (0000....0001) which is 1 decimal), otherwise 0. The Equal Comparison operation tests the two inputs (a and b). If a is equal to b then the Result would be 1 (represented as 32-bit binary number (0000.....0001) which is 1 decimal), otherwise 0. The Zero output (which is 1 bit) is 1 when all 32 bits of the Result are 0. The Overflow output (which is 1 bit) is 1 when there is an overflow in Add Sub operations. For other operations overflow is always 0. Check the outputs (Result, Carry Out, Zero, Overflow) to see if they are correct. Put a screenshot of the waveform in your report. 3 Design a 32-bit ALU The arithmetic logic unit (ALU) is the brain of the computer, the device that performs the arithmetic operations like addition and subtraction or bitwise operations like AND and OR. In this section, we want to design a 32-bit ALU. Below you see the block diagram. The Carry Out output (which is 1 bit) is set to 1 (Only in Add operation) when you have carry out on Left-most It (MSB). For other operations. Carry Out is always 0. The AND, OR, and NOR are bit-wise operations. The Set Less Than, Add, and Sub are signed operations. Signed operation can be implemented by casting value (operand) using Ssigned(). - For example: Result = Signe Dy/2. Use this simple code for your Module (Entity) detinition. ALU operation -Zero 32 Code 2: ALU module definition 1 'tinescale ina / ipa // Module definition > Iodule alu_32 (A_1n, B_1n, ALU_Se1, ALU_Out. Carry-out, Zero, Overflow): //Dafina T/O Ports ALU - Overflow bH Describe ALU behaviour cudnodulo // 32-bit ALU CarryOut Write a testbench for your design and run the tests below. th dina 32"h08fa31 test I (Run for 20ns): th din.b32"hd755F149, th alusel = "4501000" The ALU receives two 32-bita inputs (a and b) and produces one 32-bits output (Result). The ALU based on the 4-bits Control Code decides which operation should be executed. Below you can see the value of the ALU control lines and the corresponding ALU operations, ALU control lines Function 0000 AND tb din a=32 h086a1c31 test2 (Run for 20ns): tb din b=32'b10073fd1, tb alu sel = "110001" 0001 OR add tb din A-32'h08680c31 Lest3 (Run for 20ns): tb dint=32'590073fd4, tb alusel = "450010" 0010 0110 subtract tb diu a=32 1.08ba31 test 4 (Run for 20ns): tb din bs=32690073fd4, tb alu.se = "4'0110" 0111 1100 Set less than NOR tb dius=32 til 31, test 5 (Run for 20ns): tb diu_b=32'59007364, tb alusel = "4'10111" 1111 Equal comparison th_din.A 32"h08fa31 , test 6 (Run for 20ns): th_din. 32'0007344, thalusel "1100" tb din it=320661031, test 7 (Run for 20ns): tb din b=32'h0basi, tb alusel "4b1111" The Sct Less Than operation tests the two inputs (a and b). If a is less than b then the Result would he 1 (represented as 32-bit binary number (0000......0001) which is 1 decimal), cotherwise 0. The Equal Comparison operation tests the two inputs (a and b). If a isual to be then the Result would be 1 (represented as 32-bit binary number (0000....0001) which is i decimal), otherwise 0 The Zero output (which is 1 bit) is I when all 32 bits of the Result are O. The Overflow output (wlich is 1 bil) in 1 when there is an overflow in Add ur Sub operatius. For other operations overflow is always 0. test (Run for 20ns): tb din b-32'610073fd4, tb alusel "4'11" tb din a-32"h086131 Check the outputs (Result. Carry-Out, Zero, Overflow) to see if they are correct. Put a screen of the waveform in your report 4 5