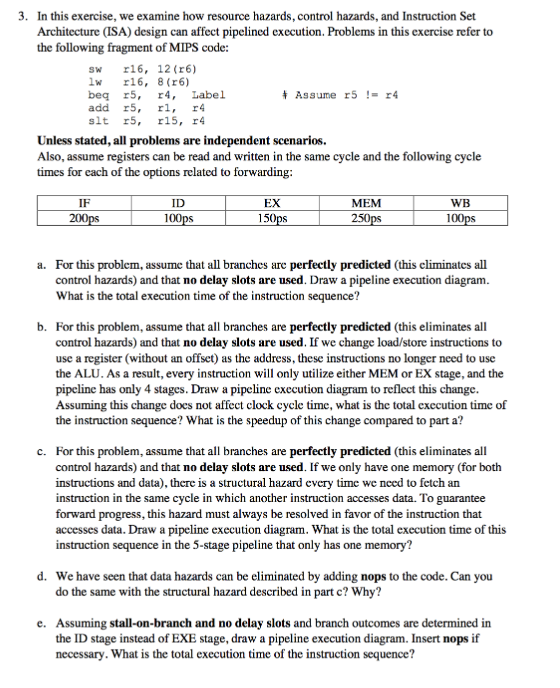

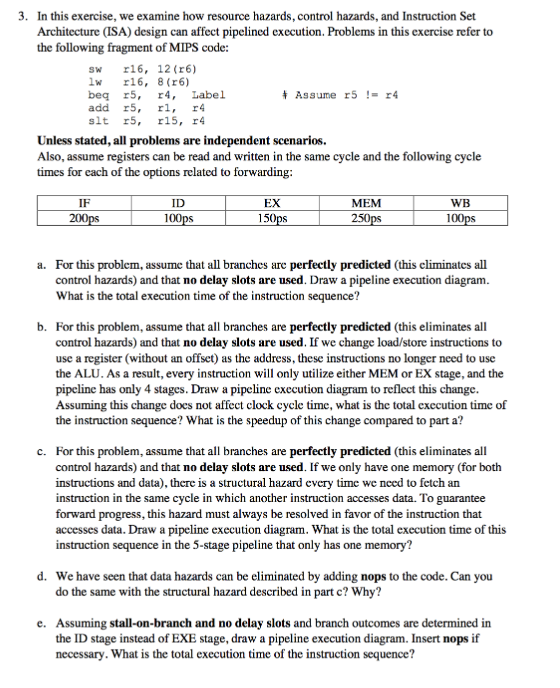

3. In this exercise, we examine how resource hazards, control hazards, and Instruction Set Architecture (ISA) design can affect pipelined execution. Problems in this exercise refer to the following fragment of MIPS code: SW 116, 12 (r6) lw r16, 8(r6) begr5, r4, Label Assume r5 != 24 add 75, rl, 14 slt 75, r15, 14 Unless stated, all problems are independent scenarios. Also, assume registers can be read and written in the same cycle and the following cycle times for each of the options related to forwarding: EX IF 200ps ID 100ps MEM 250ps WB 100ps 150ps a. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. Draw a pipeline execution diagram. What is the total execution time of the instruction sequence? b. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we change load/store instructions to use a register (without an offset) as the address, these instructions no longer need to use the ALU. As a result, every instruction will only utilize either MEM or EX stage, and the pipeline has only 4 stages. Draw a pipeline execution diagram to reflect this change. Assuming this change does not affect clock cycle time, what is the total execution time of the instruction sequence? What is the speedup of this change compared to part a? c. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we only have one memory (for both instructions and data), there is a structural hazard every time we need to fetch an instruction in the same cycle in which another instruction accesses data. To guarantee forward progress, this hazard must always be resolved in favor of the instruction that accesses data. Draw a pipeline execution diagram. What is the total execution time of this instruction sequence in the 5-stage pipeline that only has one memory? d. We have seen that data hazards can be eliminated by adding nops to the code. Can you do the same with the structural hazard described in part c? Why? c. Assuming stall-on-branch and no delay slots and branch outcomes are determined in the ID stage instead of EXE stage, draw a pipeline execution diagram. Insert nops if necessary. What is the total execution time of the instruction sequence? 3. In this exercise, we examine how resource hazards, control hazards, and Instruction Set Architecture (ISA) design can affect pipelined execution. Problems in this exercise refer to the following fragment of MIPS code: SW 116, 12 (r6) lw r16, 8(r6) begr5, r4, Label Assume r5 != 24 add 75, rl, 14 slt 75, r15, 14 Unless stated, all problems are independent scenarios. Also, assume registers can be read and written in the same cycle and the following cycle times for each of the options related to forwarding: EX IF 200ps ID 100ps MEM 250ps WB 100ps 150ps a. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. Draw a pipeline execution diagram. What is the total execution time of the instruction sequence? b. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we change load/store instructions to use a register (without an offset) as the address, these instructions no longer need to use the ALU. As a result, every instruction will only utilize either MEM or EX stage, and the pipeline has only 4 stages. Draw a pipeline execution diagram to reflect this change. Assuming this change does not affect clock cycle time, what is the total execution time of the instruction sequence? What is the speedup of this change compared to part a? c. For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we only have one memory (for both instructions and data), there is a structural hazard every time we need to fetch an instruction in the same cycle in which another instruction accesses data. To guarantee forward progress, this hazard must always be resolved in favor of the instruction that accesses data. Draw a pipeline execution diagram. What is the total execution time of this instruction sequence in the 5-stage pipeline that only has one memory? d. We have seen that data hazards can be eliminated by adding nops to the code. Can you do the same with the structural hazard described in part c? Why? c. Assuming stall-on-branch and no delay slots and branch outcomes are determined in the ID stage instead of EXE stage, draw a pipeline execution diagram. Insert nops if necessary. What is the total execution time of the instruction sequence