Question: 3. Tasks 1. Create a Vivado project for the Zybo Board 1. Let Vivado copy all the files to the project. 2. Make sure

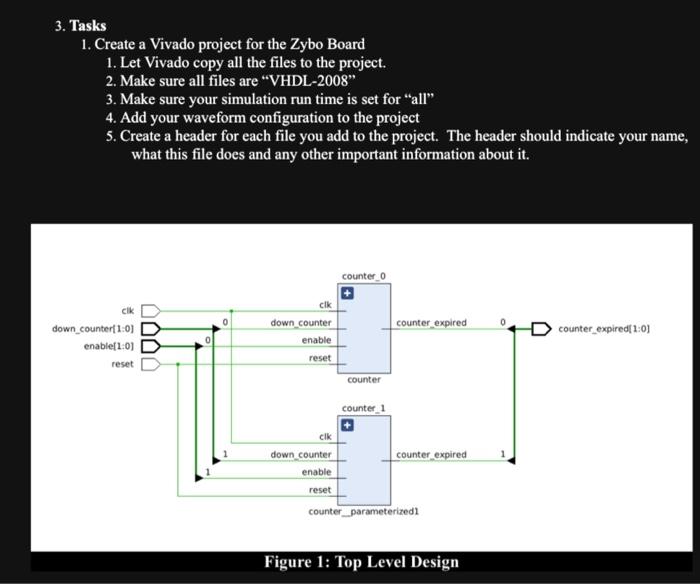

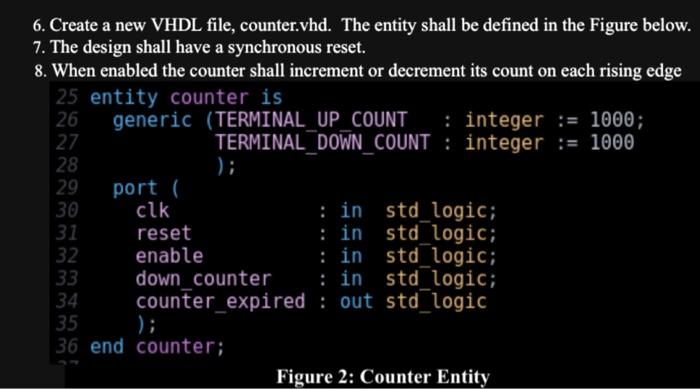

3. Tasks 1. Create a Vivado project for the Zybo Board 1. Let Vivado copy all the files to the project. 2. Make sure all files are "VHDL-2008" 3. Make sure your simulation run time is set for "all" 4. Add your waveform configuration to the project 5. Create a header for each file you add to the project. The header should indicate your name, what this file does and any other important information about it. down_counter[1:0] enable[1:0] reset 000 0 cik down counter enable reset counter 0 counter counter_1 counter_expired cik down counter enable reset counter parameterized1 counter_expired Figure 1: Top Level Design 1 counter_ expired[1:0] 6. Create a new VHDL file, counter.vhd. The entity shall be defined in the Figure below. 7. The design shall have a synchronous reset. 8. When enabled the counter shall increment or decrement its count on each rising edge 25 entity counter is 26 27 28 29 30 31 32 33 34 generic (TERMINAL UP COUNT :integer := 1000; TERMINAL_DOWN_COUNT: integer := 1000 port ( clk ); std_logic; std logic; std_logic; down_counter in std logic; counter_expired: out std logic reset enable 35 ); 36 end counter; : in : in : in : Figure 2: Counter Entity 9. When down_counter is '1', then decrement the count. When down_counter is '0', increment the count. 10. When the counter has reached the appropriate TERMINAL_XXX_COUNT value, assert the counter_expired for 1 clock cycle. 11. If the enable signal is '0', reset the count to 0 and make sure that counter_expired is'O'. 12. The generics are integers and therefore support negative values. 1. Set Counter O Generics as follows TERMINAL UP_COUNT 200 TERMINAL DOWN COUNT-100 2. Set Counter 1 Generics as follows *TERMINAL UP COUNT 20 * TERMINAL DOWN COUNT -10

Step by Step Solution

3.44 Rating (163 Votes )

There are 3 Steps involved in it

SOLUTION Here are some guidelines on how to complete the tasks you have provided Tasks 1 Create a Vivado project for the Zybo Board Open Vivado and click File New Project In the New Project dialog box ... View full answer

Get step-by-step solutions from verified subject matter experts