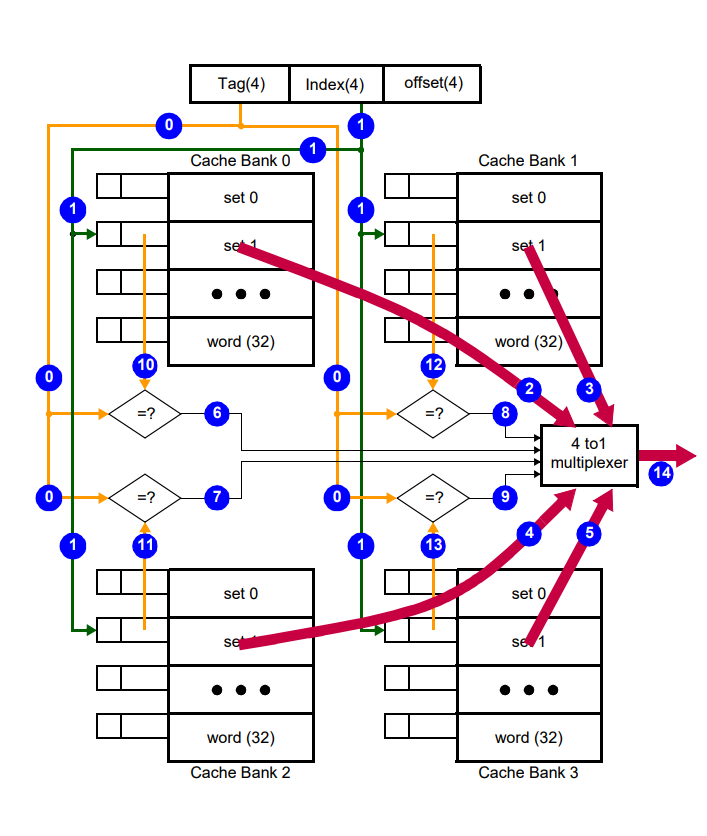

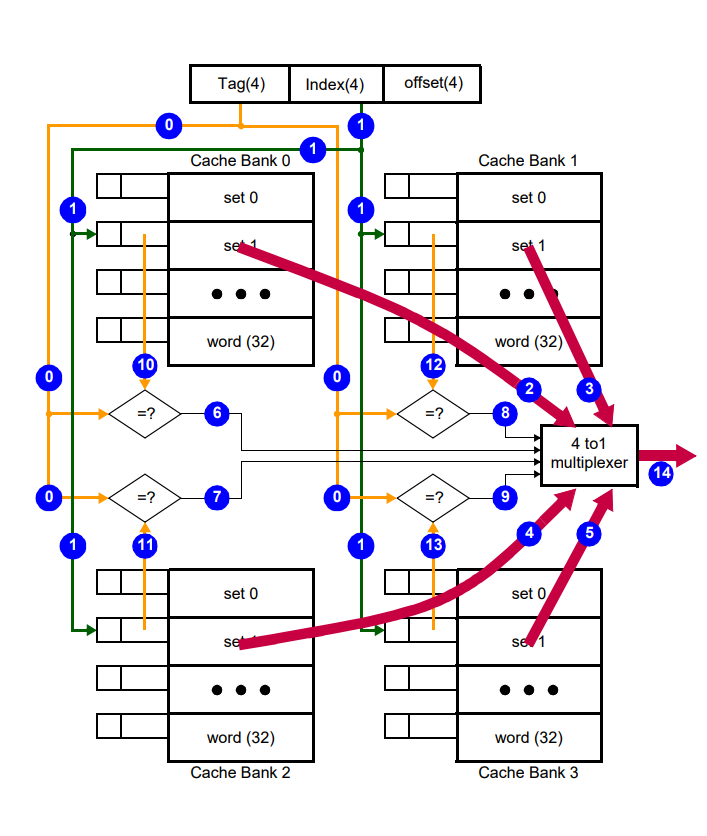

3. The figure attached shows cache memory with four-way set associative mapping. Numbers in the parentheses indicate the number of bits for each field. Note that a word is 32 bits and the cache is byte-addressable 1. Using the circled numbers, explain how you would determine cache hits/misses and find data upon cache hits 2. Find in bytes block size set size - cache bank size - cache size main memorV Size 3. The cache is initially empty. Now, CPU generates the following sequence of cache addresses in HEX: AAA, 3A2, 7A3 AA3, ??0, 7A4. 4A1, 5Al. CA2, 3Al. BBB. 4B5, 5B4. 6B3, 5B3, 5B5, 4B5, BBC, ABB, CBC. 4. Show the tag values of the corresponding set in the cache after each reference. Use LRU (Least Recently Used) policy for block replacement. LRU replaces the one that was least recently used with the new one 5. Find the number of blocks to be replaced for the above mapping scheme 6. Find the number of cache misses including compulsory misses 7. Find the number of cache hits. 8. Not required to do at this time but something to think about: Can you handle for 2-way set associative mapping Everything remains the same but the cache is now organized such that two tags are checked simultaneously 3. The figure attached shows cache memory with four-way set associative mapping. Numbers in the parentheses indicate the number of bits for each field. Note that a word is 32 bits and the cache is byte-addressable 1. Using the circled numbers, explain how you would determine cache hits/misses and find data upon cache hits 2. Find in bytes block size set size - cache bank size - cache size main memorV Size 3. The cache is initially empty. Now, CPU generates the following sequence of cache addresses in HEX: AAA, 3A2, 7A3 AA3, ??0, 7A4. 4A1, 5Al. CA2, 3Al. BBB. 4B5, 5B4. 6B3, 5B3, 5B5, 4B5, BBC, ABB, CBC. 4. Show the tag values of the corresponding set in the cache after each reference. Use LRU (Least Recently Used) policy for block replacement. LRU replaces the one that was least recently used with the new one 5. Find the number of blocks to be replaced for the above mapping scheme 6. Find the number of cache misses including compulsory misses 7. Find the number of cache hits. 8. Not required to do at this time but something to think about: Can you handle for 2-way set associative mapping Everything remains the same but the cache is now organized such that two tags are checked simultaneously