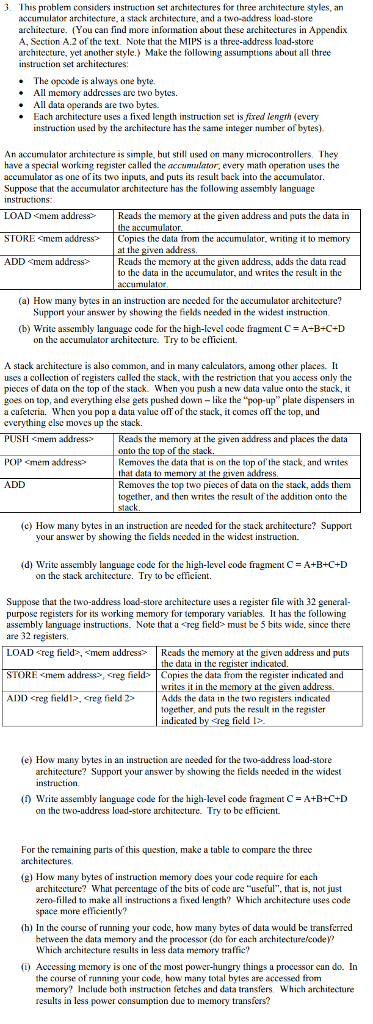

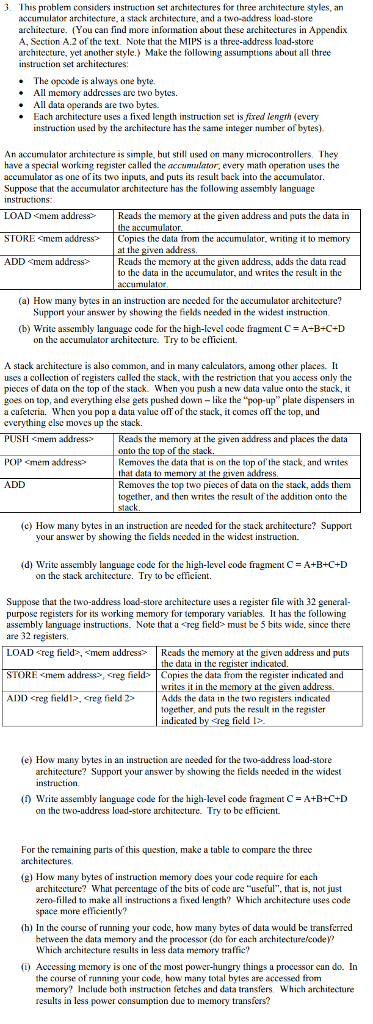

3. This problem considers instruction set architectures for three architecture styles, an accumulator architecture, a stack architecture, and a two-address load-store architecture. (You can find more information about these architectures in Appendix A, Section A.2 of the text. Note that the MIPS is a three-address load-store architecture, yet another style.) Make the following assumptions about all three instruction set architectures: The opcode is always one byte All memory addresses are two bytes. All data operands are two bytes. Each architecture uses a fixed length instruction set is fixed length (every instruction used by the architecture has the same integer number of bytes) An accumulator architecture is simple, but still used on many microcontllers. They have a special working register called the accumulator, every math operation uses the accumulator as one of its two inputs, and puts its result back into the accumulator. Suppose that the accumulator architecture has the following assembly language LOAD mem addressReads the memory at the given address and puts the data in STORE -mem address Copies the data from the accumulator, writing it to memory ADD

the accumulator address at the Reads the memory t the given address, adds the data read to the data in the uccumulutor, and writes the result in the (a) How many bytes in an instruction are nceded for the accumulator architccture? Support your answer by showing the fields needed in the widest instruction. (b) Write assembly language code for the high-level code fragment C A-B-C-D on the accumulator architecture. Try to be efficient. A stack architecture is also common, and in many caleulators, among otber places. It uses a collection of registers culled the stack, with the restriction that you access only the pieces of data on the top ofthe stack, when you push new data value onto the stack, it goes on top, and everything else gets pushed down -like the "pop-up" plate dispensers in a cafeteria. When you pop a data valuc off of the stack, it comes off the top, and everything else moves up the stack. PUSH mem address:>Reads the memory at the given address and places the data POP mem address ADD onto the top of the stack. Removes the data that is on the top of the stack, and writes that data to Removes the top two pieces of data on the stack, adds them together, and then writes the result of the addition onto the stack at the address (c How many bytes in an instruction are nceded for the stack architecture? Support your answer by showing the ficlds nceded in the widest instruction. (d) Write assembly language code for the high-level code fragment C = A+B+C+D on the stack architecture. Try to be efficient. Suppose that the two-address load-store architecture uses a register file with 32 general purpose registers for its working memory for temporury variables. It has the following assembly language instructions. Note that a reg field must be 5 bits wide, since there LOAD reg field*, , creg field Copies the data from the register indicated a AlDI) creg fieldl, reg field 2 the datu in the rerister indicated writes it in the memory at the given Adds the data in the two registers indicated together, and puts the result in the register address. field > (e) How many bytes in an instruction are needed for the two-address load-store architecture? Support your answer by showing the fields needed in the widest (f) Write assembly language code for the high-level code fragment C = A+B+C+D on the two-address load-store architecture. Try to be eflicient For the remaining parts of this question, make a table to compare the three (g) How many bytes of instruction memory does your code require for each architecture? What percentage of the bits of code arc "uscful", that is, not just ero-filled to make all instructions a fixed length? Which architecture uses code space more efficiently? (h) In the course of running your code, how many bytes of data would be transferred between the data memory and the processor (do for each architecture/code)? Which architecture results in less data memory traffic? (i) Accessing memory is onc of the most power-hungry things a processor can do. In the course of running your code, how many total bytes are accessed from memory? Include both instruction fetches and data transfers Which architecture results in less power consumption due to memory transfers