Question: 4. (33 pts.) A superscalar computer has Level 1 split Data and Instruction Caches, Level 2 (Combined) Cache, Main Memory, and a Hard Disk. The

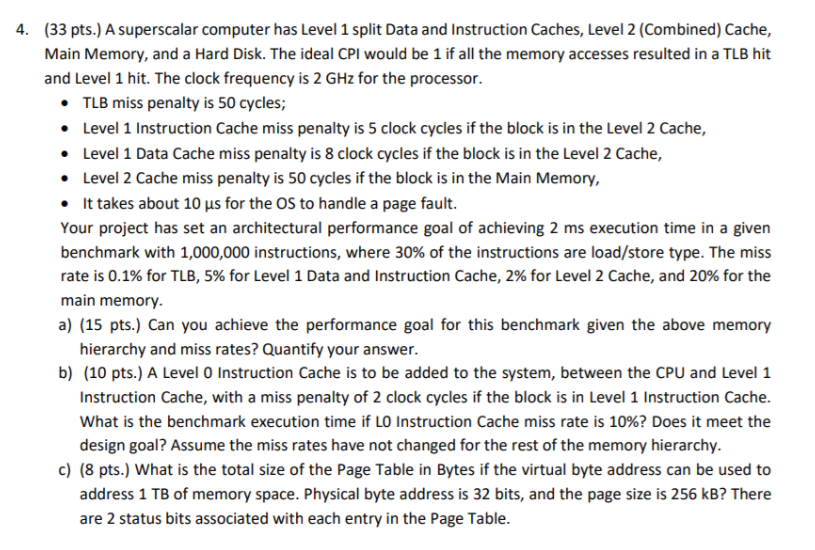

4. (33 pts.) A superscalar computer has Level 1 split Data and Instruction Caches, Level 2 (Combined) Cache, Main Memory, and a Hard Disk. The ideal CPI would be 1 if all the memory accesses resulted in a TLB hit and Level 1 hit. The clock frequency is 2 GHz for the processor. TLB miss penalty is 50 cycles; Level 1 Instruction Cache miss penalty is 5 clock cycles if the block is in the Level 2 Cache, Level 1 Data Cache miss penalty is 8 clock cycles if the block is in the Level 2 Cache, Level 2 Cache miss penalty is 50 cycles if the block is in the Main Memory, It takes about 10 us for the OS to handle a page fault. Your project has set an architectural performance goal of achieving 2 ms execution time in a given benchmark with 1,000,000 instructions, where 30% of the instructions are load/store type. The miss rate is 0.1% for TLB, 5% for Level 1 Data and Instruction Cache, 2% for Level 2 Cache, and 20% for the main memory. a) (15 pts.) Can you achieve the performance goal for this benchmark given the above memory hierarchy and miss rates? Quantify your answer. b) (10 pts.) A Level 0 Instruction Cache is to be added to the system, between the CPU and Level 1 Instruction Cache, with a miss penalty of 2 clock cycles if the block is in Level 1 Instruction Cache. What is the benchmark execution time if Lo Instruction Cache miss rate is 10%? Does it meet the design goal? Assume the miss rates have not changed for the rest of the memory hierarchy. c) (8 pts.) What is the total size of the Page Table in Bytes if the virtual byte address can be used to address 1 TB of memory space. Physical byte address is 32 bits, and the page size is 256 kB? There are 2 status bits associated with each entry in the Page Table. 4. (33 pts.) A superscalar computer has Level 1 split Data and Instruction Caches, Level 2 (Combined) Cache, Main Memory, and a Hard Disk. The ideal CPI would be 1 if all the memory accesses resulted in a TLB hit and Level 1 hit. The clock frequency is 2 GHz for the processor. TLB miss penalty is 50 cycles; Level 1 Instruction Cache miss penalty is 5 clock cycles if the block is in the Level 2 Cache, Level 1 Data Cache miss penalty is 8 clock cycles if the block is in the Level 2 Cache, Level 2 Cache miss penalty is 50 cycles if the block is in the Main Memory, It takes about 10 us for the OS to handle a page fault. Your project has set an architectural performance goal of achieving 2 ms execution time in a given benchmark with 1,000,000 instructions, where 30% of the instructions are load/store type. The miss rate is 0.1% for TLB, 5% for Level 1 Data and Instruction Cache, 2% for Level 2 Cache, and 20% for the main memory. a) (15 pts.) Can you achieve the performance goal for this benchmark given the above memory hierarchy and miss rates? Quantify your answer. b) (10 pts.) A Level 0 Instruction Cache is to be added to the system, between the CPU and Level 1 Instruction Cache, with a miss penalty of 2 clock cycles if the block is in Level 1 Instruction Cache. What is the benchmark execution time if Lo Instruction Cache miss rate is 10%? Does it meet the design goal? Assume the miss rates have not changed for the rest of the memory hierarchy. c) (8 pts.) What is the total size of the Page Table in Bytes if the virtual byte address can be used to address 1 TB of memory space. Physical byte address is 32 bits, and the page size is 256 kB? There are 2 status bits associated with each entry in the Page Table

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts