Answered step by step

Verified Expert Solution

Question

1 Approved Answer

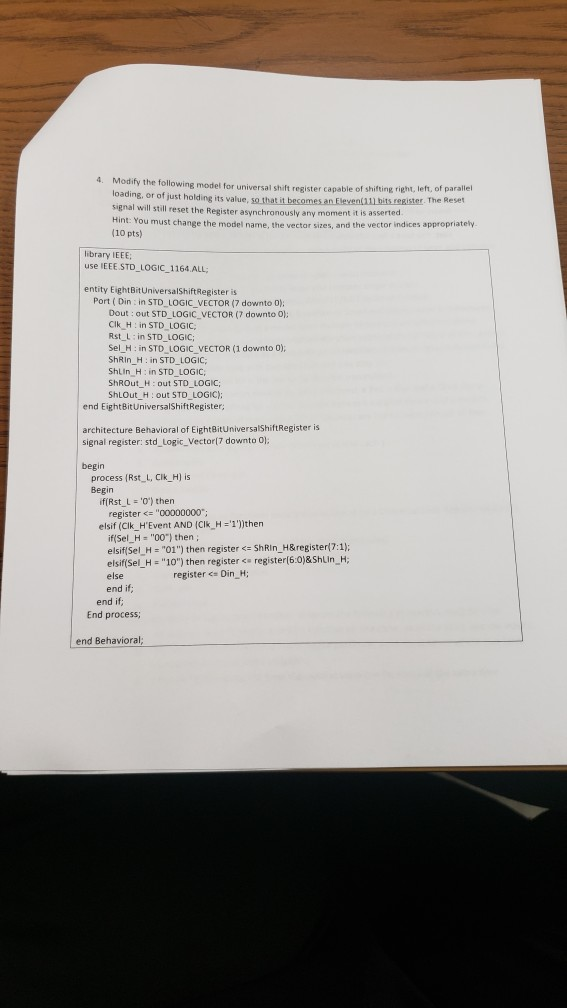

4 Modify the following model for universal shift register capable of shifting right left of parallel loading, or of just holding its value, so that

4 Modify the following model for universal shift register capable of shifting right left of parallel loading, or of just holding its value, so that it becomes an Eleven this register. The Reset signal will still reset the Register asynchronously any moment it is asserted Hint: You must change the model name the vertar sizes and the vector indices appropriately (10 pts) library IEEE use IEEE STD_LOGIC_1164 ALL; entity EightBitUniversalShift Register is Port (Din: in STD_LOGIC_VECTOR (7 downto 0); Dout: out STD_LOGIC_VECTOR (7 downto 0); Cik Hin STD LOGIC Rst L: in STD_LOGIC; Sel_H : in STD LOGIC_VECTOR (1 downto 0); ShRin_H: in STD_LOGIC Shlin H:in STD_LOGIC, ShRout_Hout STD LOGIC; Shlout_H : out STO_LOGIC); end EightBit UniversalShift Register, architecture Behavioral of EightBitUniversalShift Register is signal register: std_logic_Vector (7 downto 0) begin process (Rst_L, CIK H) is Begin if Rst L = '0') then register

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started