Question

4.3 When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following three problems,

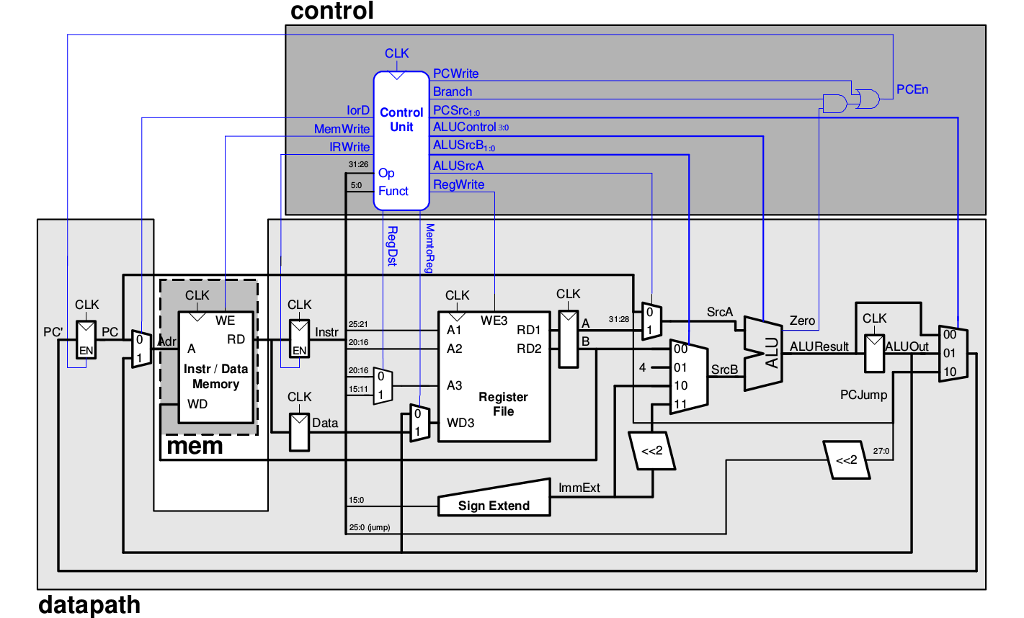

4.3 When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following three problems, assume that we are starting with a datapath from Figure 4.2 , where I-Mem, Add, Mux, ALU, Regs, D-Mem, and Control blocks have latencies of 400 ps, 100 ps, 30 ps, 120 ps, 200 ps, 350 ps, and 100 ps, respectively, and costs of 1000, 30, 10, 100, 200, 2000, and 500, respectively.

Consider the addition of a multiplier to the ALU. This addition will add 300 ps to the latency of the ALU and will add a cost of 600 to the ALU. The result will be 5% fewer instructions executed since we will no longer need to emulate the MUL instruction.

4.3.1 [10] What is the clock cycle time with and without this improvement?

4.3.2 [10] What is the speedup achieved by adding this improvement?

4.3.3 [10] Compare the cost/performance ratio with and without this improvement.

CLK CLK WE PC PC 0 Ad RD nstr Data Memory WD mem datapath control CLK PC Write Branch or D Control PCSrc10 Unit ALUControl 30 Mem Write ALUSrcB1 RWrite 31:28 op ALUSrCA. RegWrite 5:0 Funct CLK CLK WE3 25:2 A1 RD nstr RD2 EN 20:16 A3 CLK Register File Data WD3 5:0 Sign Extend 25.0 Gump) CLK 31:28 mmExtStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started