Answered step by step

Verified Expert Solution

Question

1 Approved Answer

5 . 1 1 This exercise examines the effect of different cache designs, specifically comparing associative caches to the direct - mapped caches from Section

This exercise examines the effect of different cache designs, specifically comparing associative caches to the directmapped caches from Section For these exercises, refer to the sequence of word address shown below.

xbe,

xce

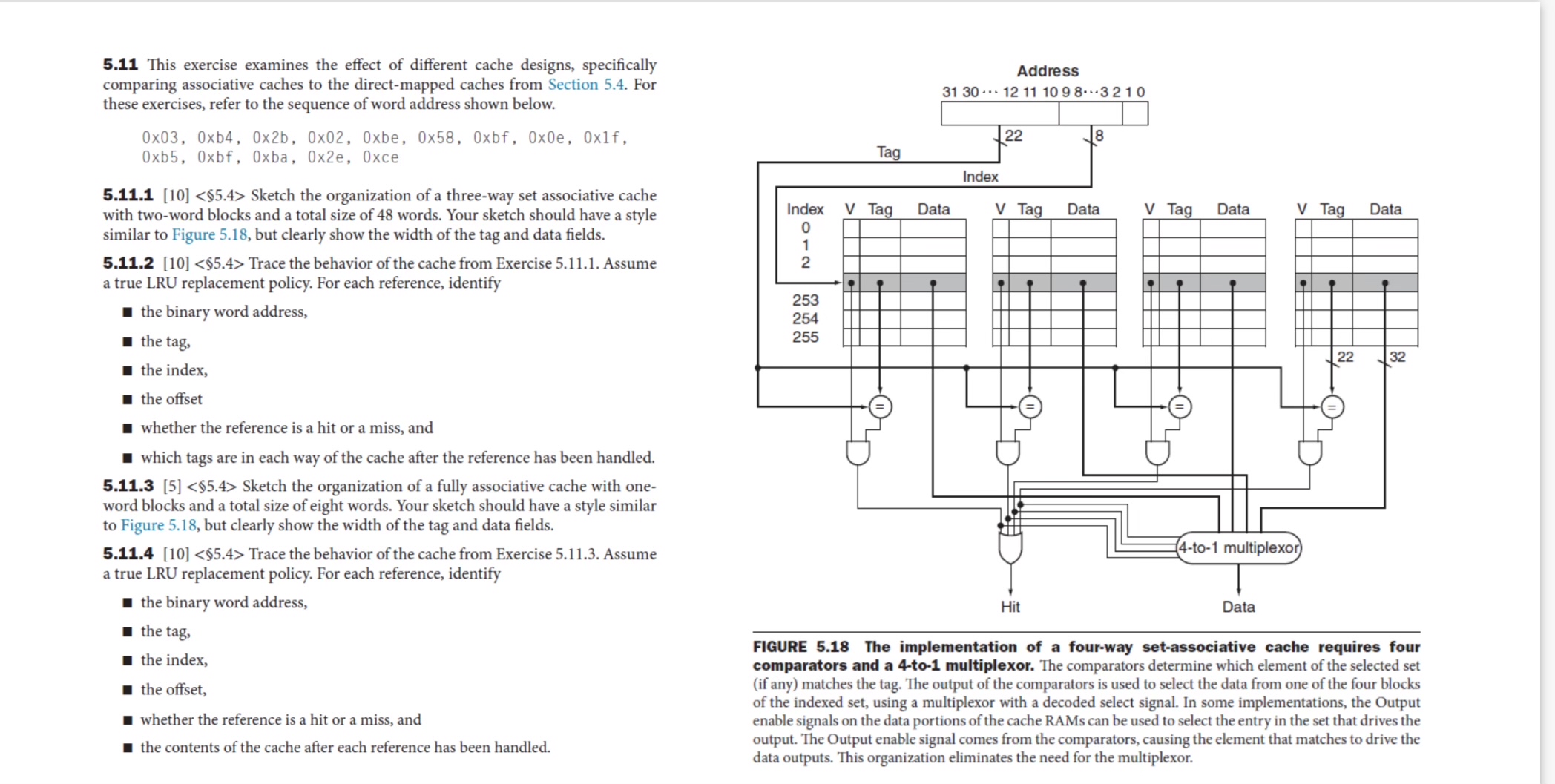

$ Sketch the organization of a threeway set associative cache with twoword blocks and a total size of words. Your sketch should have a style similar to Figure but clearly show the width of the tag and data fields.

$ Trace the behavior of the cache from Exercise Assume a true LRU replacement policy. For each reference, identify

the binary word address,

the tag,

the index,

the offset

whether the reference is a hit or a miss, and

which tags are in each way of the cache after the reference has been handled.

Sketch the organization of a fully associative cache with oneword blocks and a total size of eight words. Your sketch should have a style similar to Figure but clearly show the width of the tag and data fields.

$ Trace the behavior of the cache from Exercise Assume a true LRU replacement policy. For each reference, identify

the binary word address,

the tag,

the index,

the offset,

whether the reference is a hit or a miss, and

the contents of the cache after each reference has been handled.

Address

FIGURE The implementation of a fourway setassociative cache requires four comparators and a to multiplexor. The comparators determine which element of the selected set if any matches the tag. The output of the comparators is used to select the data from one of the four blocks of the indexed set, using a multiplexor with a decoded select signal. In some implementations, the Output enable signals on the data portions of the cache RAMs can be used to select the entry in the set that drives the output. The Output enable signal comes from the comparators, causing the element that matches to drive the data outputs. This organization eliminates the need for the multiplexor.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started