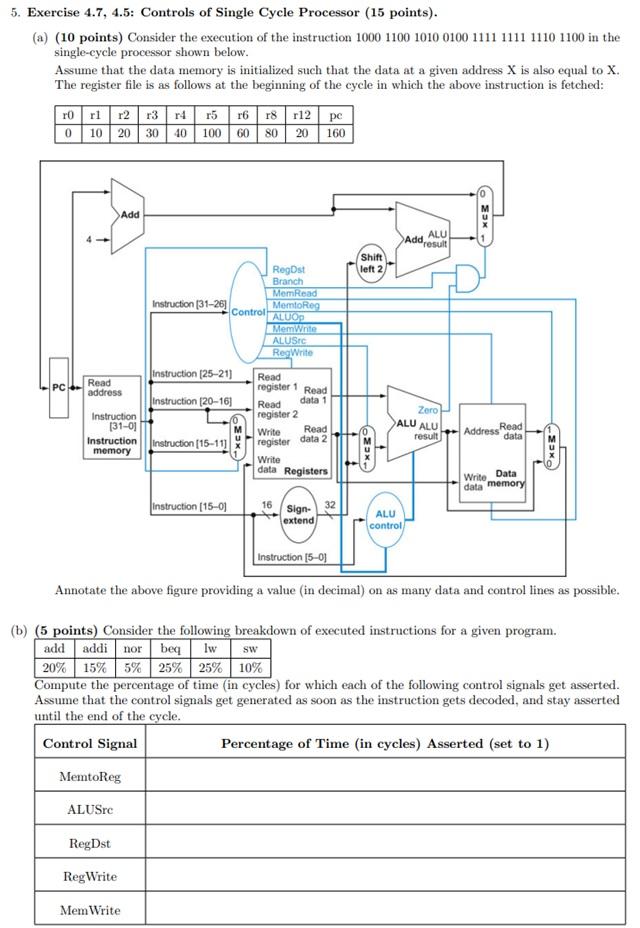

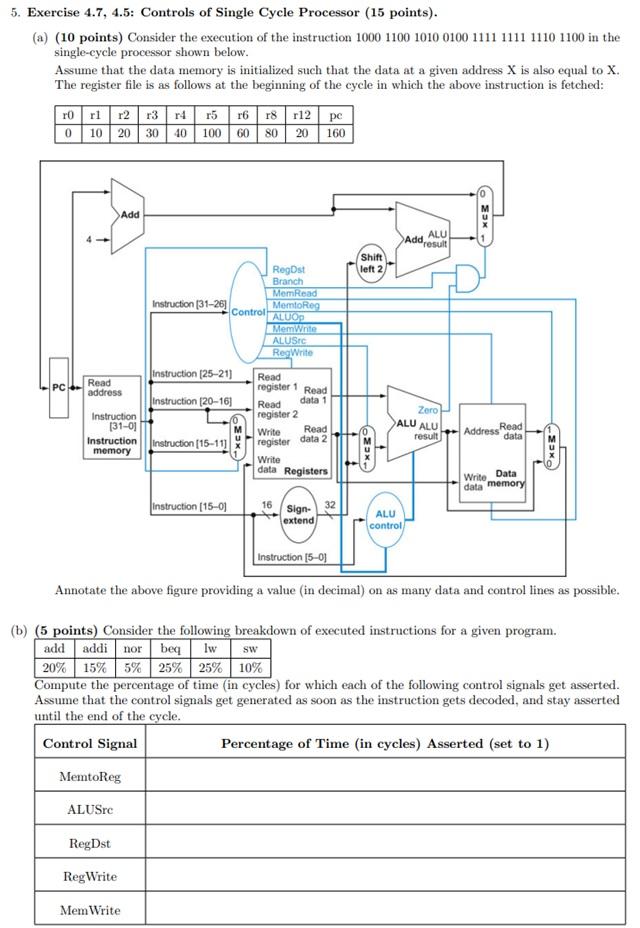

5. Exercise 4.7, 4.5: Controls of Single Cycle Processor (15 points). (a) (10 points) Consider the execution of the instruction 1000 1100 1010 0100 1111 1111 1110 1100 in the single-cycle processor shown below. Assume that the data memory is initialized such that the data at a given address X is also equal to X. The register file is as follows at the beginning of the cycle in which the above instruction is fetched: rort r2 13 14 15 r6 r8 r12 0 10 20 30 40 100 60 160 80 20 Add XES ALU Add result Shift left 2 RegDst Branch MemRead Instruction (31-26] Momto Reg Control ALUOD Mem Wate ALUSIC RegWrite instruction (25-21) Read register 1 Read Instruction (20-16 Read data 1 register 2 Write Read Instruction (15-11] data 2 register Write data Registers PC Read address Zero ALU ALU Instruction (31-0 Instruction memory 2x Address Read data result ox Write Data data memory instruction (15-01 16 Sign- 32 extend ALU control Instruction (5-0) Annotate the above figure providing a value (in decimal) on as many data and control lines as possible. SW (b) (5 points) Consider the following breakdown of executed instructions for a given program. add addi nor beq lw 20% 15% 5% 25% 25% 10% Compute the percentage of time (in cycles) for which each of the following control signals get asserted. Assume that the control signals get generated as soon as the instruction gets decoded, and stay asserted until the end of the cycle. Control Signal Percentage of Time (in cycles) Asserted (set to 1) MemtoReg ALUS RegDst Reg Write Mem Write 5. Exercise 4.7, 4.5: Controls of Single Cycle Processor (15 points). (a) (10 points) Consider the execution of the instruction 1000 1100 1010 0100 1111 1111 1110 1100 in the single-cycle processor shown below. Assume that the data memory is initialized such that the data at a given address X is also equal to X. The register file is as follows at the beginning of the cycle in which the above instruction is fetched: rort r2 13 14 15 r6 r8 r12 0 10 20 30 40 100 60 160 80 20 Add XES ALU Add result Shift left 2 RegDst Branch MemRead Instruction (31-26] Momto Reg Control ALUOD Mem Wate ALUSIC RegWrite instruction (25-21) Read register 1 Read Instruction (20-16 Read data 1 register 2 Write Read Instruction (15-11] data 2 register Write data Registers PC Read address Zero ALU ALU Instruction (31-0 Instruction memory 2x Address Read data result ox Write Data data memory instruction (15-01 16 Sign- 32 extend ALU control Instruction (5-0) Annotate the above figure providing a value (in decimal) on as many data and control lines as possible. SW (b) (5 points) Consider the following breakdown of executed instructions for a given program. add addi nor beq lw 20% 15% 5% 25% 25% 10% Compute the percentage of time (in cycles) for which each of the following control signals get asserted. Assume that the control signals get generated as soon as the instruction gets decoded, and stay asserted until the end of the cycle. Control Signal Percentage of Time (in cycles) Asserted (set to 1) MemtoReg ALUS RegDst Reg Write Mem Write