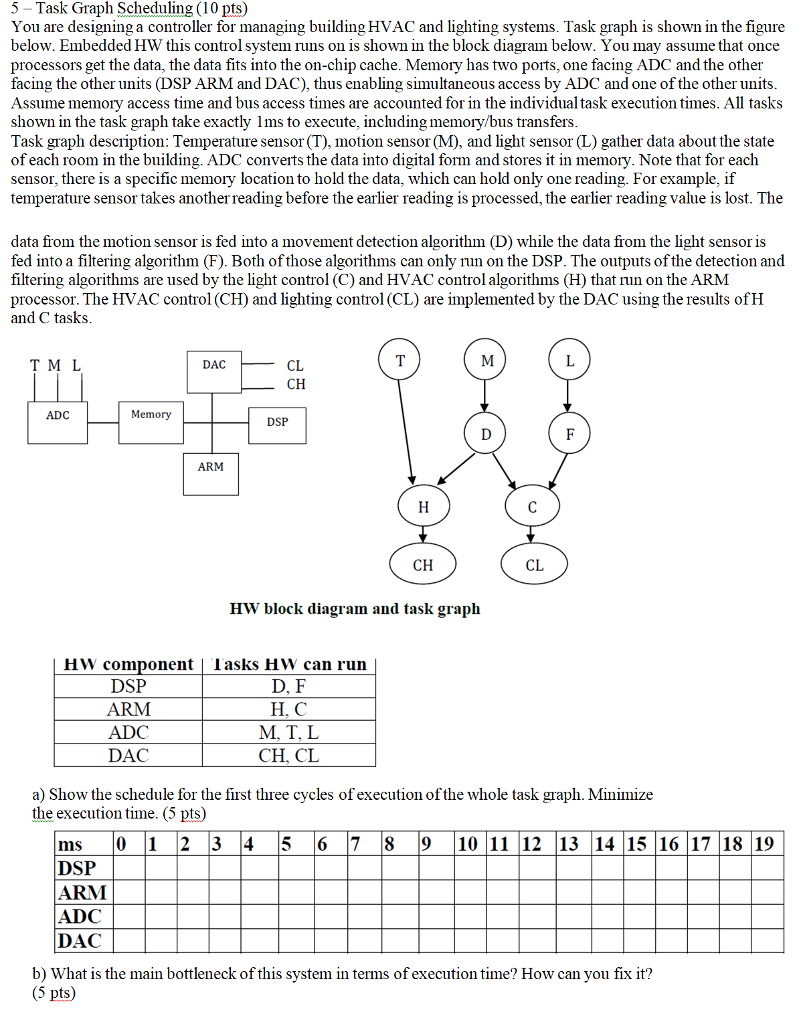

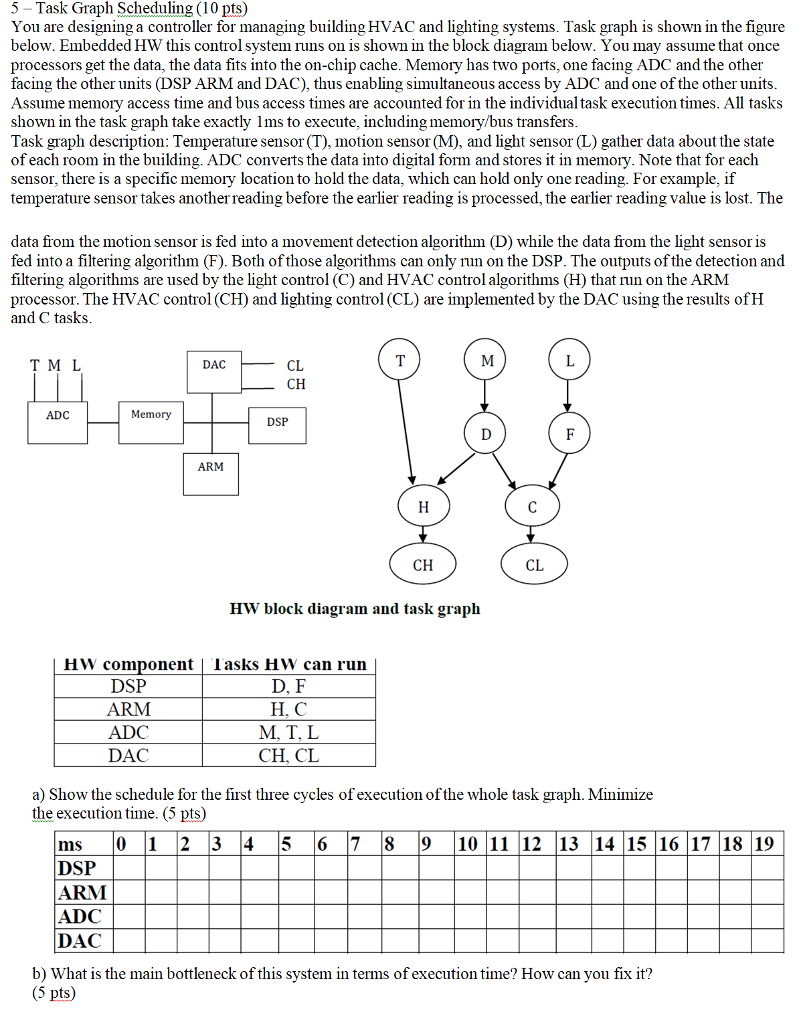

5 - Task Graph Scheduling (10 pts) You are designing a controller for managing building HVAC and lighting systems. Task graph is shown in the figure below. Embedded HW this control system runs on is shown in the block diagram below. You may assume that once processors get the data, the data fits into the on-chip cache. Memory has two ports, one facing ADC and the other facing the other units (DSP ARM and DAC), thus enabling simultaneous access by ADC and one of the other units Assume memory access time and bus access times are accounted for in the individual task execution times. All tasks shown in the task graph take exactly lms to execute, including memory/bus transfers Task graph description: Temperature sensor (T), motion sensor (M), and light sensor (L) gather data about the state of each room in the building. ADC converts the data into digital form and stores it in memory. Note that for each sensor, there is a specific memory location to hold the data, which can hold only one reading. For example, if temperature sensor takes another reading before the earlier reading is processed, the earlier reading value is lost. The data from the motion sensor is fed into a movement detection algorithm (D) while the data from the light sensor is fed into a filtering algorithm (F). Both of those algorithms can only run on the DSP. The outputs of the detection and filtering algorithms are used by the light control (C) and HVAC control algorithms (H) that run on the ARM processor. The HVAC control (CH) and lighting control (CL) are implemented by the DAC using the results ofH and C tasks T M L DAC CL CH ADC Memory DSP ARM CH CL HW block diagram and task graph HW component Tasks HW can run DSP ARM ADC DAC D. F H. C M, T. L CH, CL a) Show the schedule for the first three cycles of execution ofthe whole task graph. Minimize the execution time. (5 pts) ms 01 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 DSP ARM ADC DAC b) What is the main bottleneck of this system in terms of execution time? How can you fix it? (5 pts) 5 - Task Graph Scheduling (10 pts) You are designing a controller for managing building HVAC and lighting systems. Task graph is shown in the figure below. Embedded HW this control system runs on is shown in the block diagram below. You may assume that once processors get the data, the data fits into the on-chip cache. Memory has two ports, one facing ADC and the other facing the other units (DSP ARM and DAC), thus enabling simultaneous access by ADC and one of the other units Assume memory access time and bus access times are accounted for in the individual task execution times. All tasks shown in the task graph take exactly lms to execute, including memory/bus transfers Task graph description: Temperature sensor (T), motion sensor (M), and light sensor (L) gather data about the state of each room in the building. ADC converts the data into digital form and stores it in memory. Note that for each sensor, there is a specific memory location to hold the data, which can hold only one reading. For example, if temperature sensor takes another reading before the earlier reading is processed, the earlier reading value is lost. The data from the motion sensor is fed into a movement detection algorithm (D) while the data from the light sensor is fed into a filtering algorithm (F). Both of those algorithms can only run on the DSP. The outputs of the detection and filtering algorithms are used by the light control (C) and HVAC control algorithms (H) that run on the ARM processor. The HVAC control (CH) and lighting control (CL) are implemented by the DAC using the results ofH and C tasks T M L DAC CL CH ADC Memory DSP ARM CH CL HW block diagram and task graph HW component Tasks HW can run DSP ARM ADC DAC D. F H. C M, T. L CH, CL a) Show the schedule for the first three cycles of execution ofthe whole task graph. Minimize the execution time. (5 pts) ms 01 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 DSP ARM ADC DAC b) What is the main bottleneck of this system in terms of execution time? How can you fix it? (5 pts)