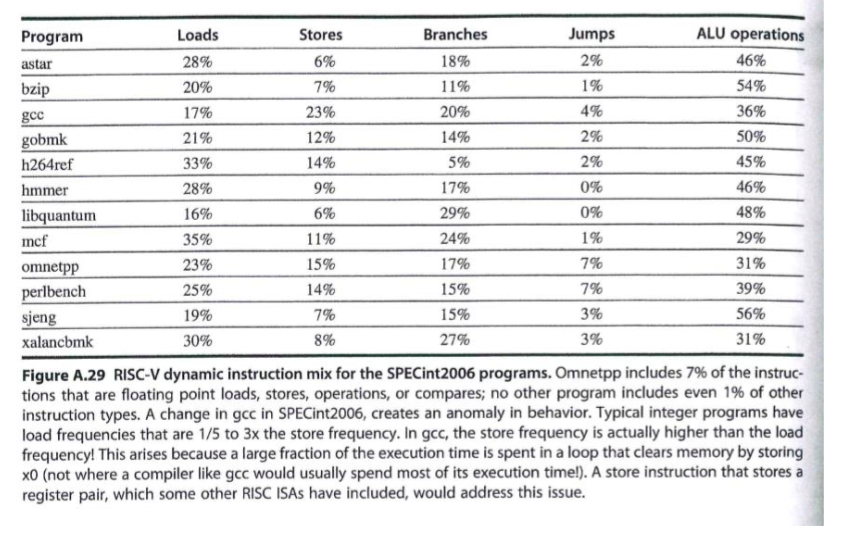

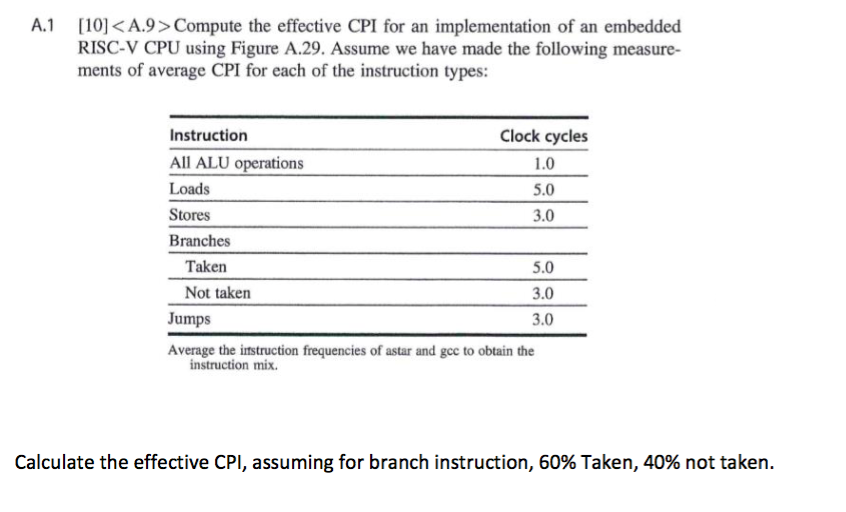

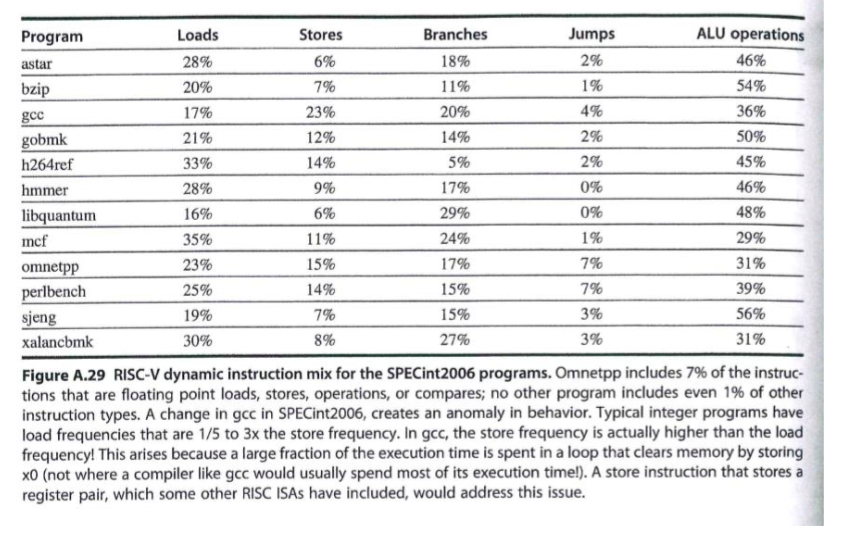

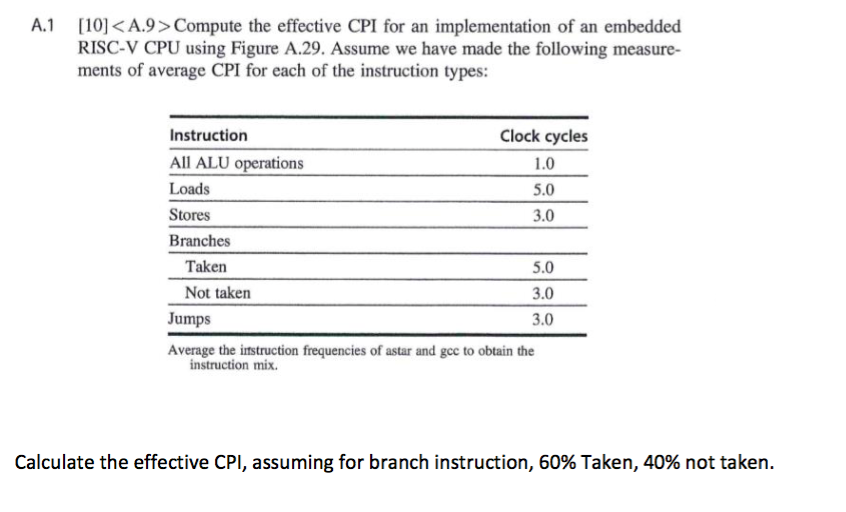

6% mcf 24% 29% Program Loads Stores Branches Jumps ALU operations astar 28% 18% 2% 46% bzip 20% 7% 11% 1% 54% gcc 17% 23% 20% 49% 36% gobmk 21% 12% 14% 2% 50% h264ref 33% 14% 5% 2% 45% hmmer 28% 9% 17% 0% 469% libquantum 16% 69% 29% 0% 48% 35% 11% 1% omnetpp 23% 15% 17% 31% perlbench 25% 14% 15% 7% 39% sjeng 19% 7% 15% 3% 56% xalancbmk 30% 8% 27% 39% 31% Figure A.29 RISC-V dynamic instruction mix for the SPECint2006 programs. Omnetpp includes 7% of the instruc- tions that are floating point loads, stores, operations, or compares; no other program includes even 19% of other instruction types. A change in gcc in SPECint2006, creates an anomaly in behavior. Typical integer programs have load frequencies that are 1/5 to 3x the store frequency. In gcc, the store frequency is actually higher than the load frequency! This arises because a large fraction of the execution time is spent in a loop that clears memory by storing x0 (not where a compiler like gcc would usually spend most of its execution timel). A store instruction that stores a register pair, which some other RISC ISAs have included, would address this issue. 7% 6% mcf 24% 29% Program Loads Stores Branches Jumps ALU operations astar 28% 18% 2% 46% bzip 20% 7% 11% 1% 54% gcc 17% 23% 20% 49% 36% gobmk 21% 12% 14% 2% 50% h264ref 33% 14% 5% 2% 45% hmmer 28% 9% 17% 0% 469% libquantum 16% 69% 29% 0% 48% 35% 11% 1% omnetpp 23% 15% 17% 31% perlbench 25% 14% 15% 7% 39% sjeng 19% 7% 15% 3% 56% xalancbmk 30% 8% 27% 39% 31% Figure A.29 RISC-V dynamic instruction mix for the SPECint2006 programs. Omnetpp includes 7% of the instruc- tions that are floating point loads, stores, operations, or compares; no other program includes even 19% of other instruction types. A change in gcc in SPECint2006, creates an anomaly in behavior. Typical integer programs have load frequencies that are 1/5 to 3x the store frequency. In gcc, the store frequency is actually higher than the load frequency! This arises because a large fraction of the execution time is spent in a loop that clears memory by storing x0 (not where a compiler like gcc would usually spend most of its execution timel). A store instruction that stores a register pair, which some other RISC ISAs have included, would address this issue. 7%