Answered step by step

Verified Expert Solution

Question

1 Approved Answer

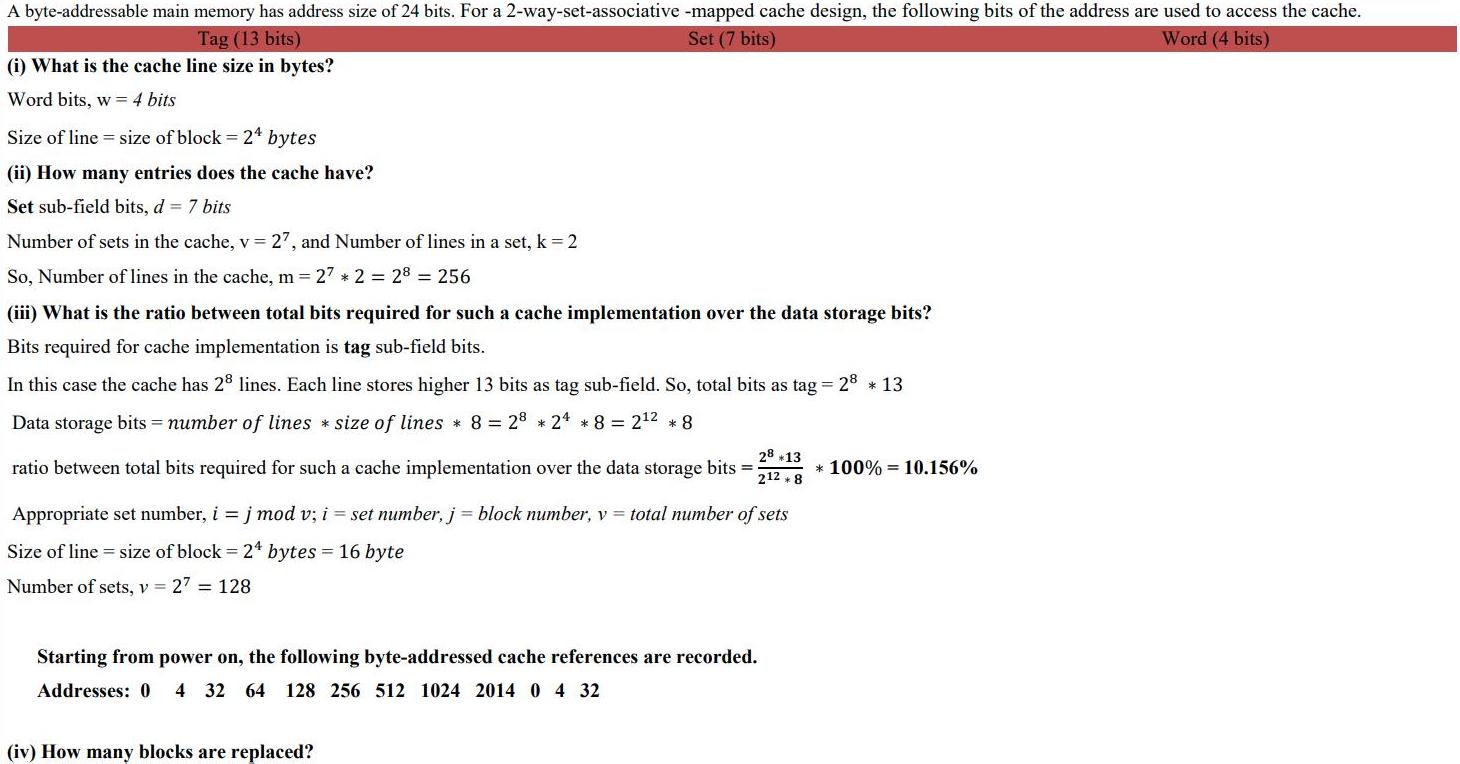

A byte-addressable main memory has address size of 24 bits. For a 2-way-set-associative -mapped cache design, the following bits of the address are used

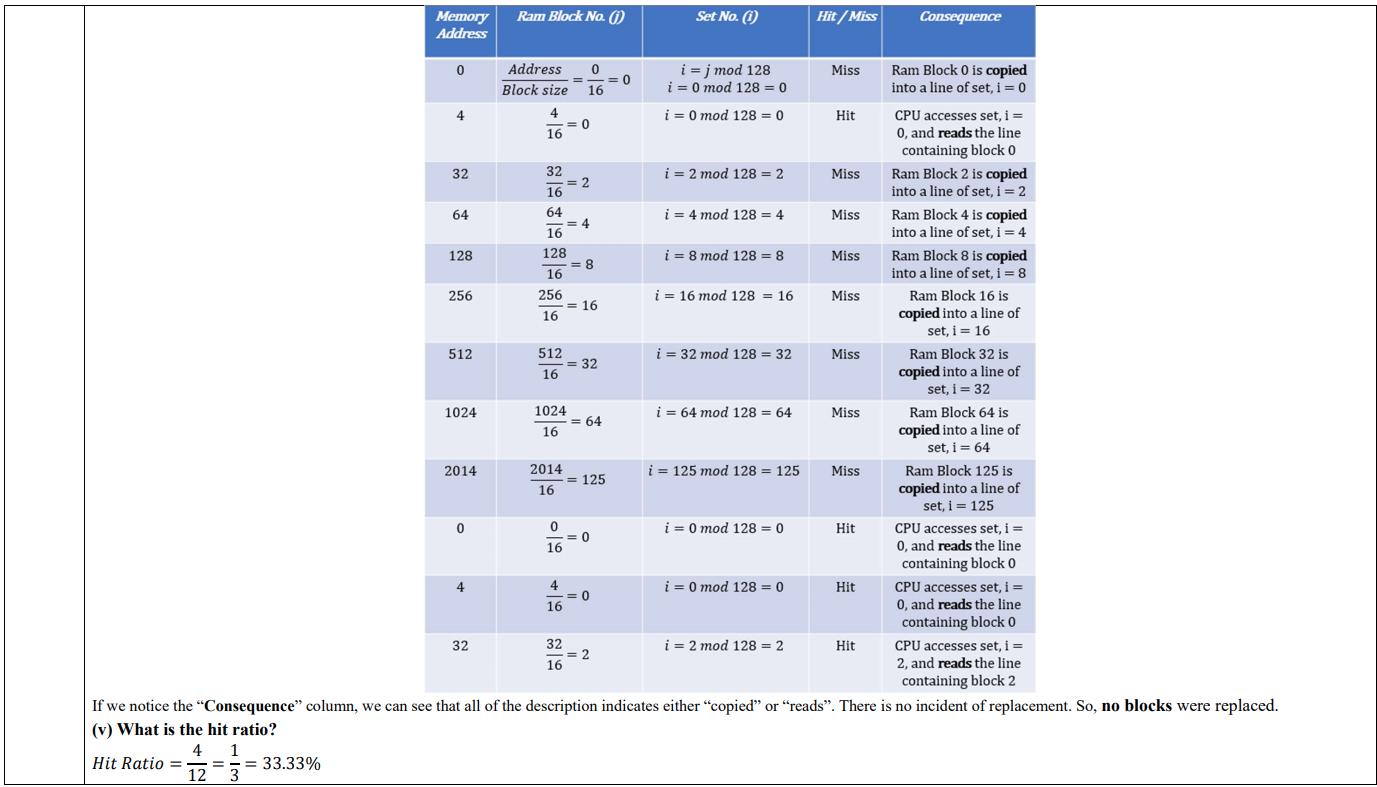

A byte-addressable main memory has address size of 24 bits. For a 2-way-set-associative -mapped cache design, the following bits of the address are used to access the cache. Tag (13 bits) (i) What is the cache line size in bytes? Set (7 bits) Word (4 bits) Word bits, w = 4 bits Size of line = size of block = 2* bytes (ii) How many entries does the cache have? Set sub-field bits, d = 7 bits Number of sets in the cache, v = 2", and Number of lines in a set, k = 2 So, Number of lines in the cache, m = 27 * 2 = 28 = 256 (iii) What is the ratio between total bits required for such a cache implementation over the data storage bits? Bits required for cache implementation is tag sub-field bits. In this case the cache has 28 lines. Each line stores higher 13 bits as tag sub-field. So, total bits as tag = 28 * 13 Data storage bits number of lines * size of lines * 8 = 28 *24 * 8 = 212 *8 28 13 ratio between total bits required for such a cache implementation over the data storage bits = * 100% = 10.156% 212 8 Appropriate set number, i = jmod v; i = set number, j = block number, v = total number of sets Size of line = size of block =2* bytes = 16 byte Number of sets, v = 27 = 128 Starting from power on, the following byte-addressed cache references are recorded. Addresses: 0 4 32 64 128 256 512 1024 2014 0 4 32 (iv) How many blocks are replaced? Memory Address Set No. 1) Hit /Miss Ram Block No. () Consequence i = j mod 128 i = 0 mod 128 = 0 Address Ram Block 0 is copied into a line of set, i = 0 Miss Block size 16 i = 0 mod 128 = 0 CPU accesses set, i = 0, and reads the line containing block 0 4 Hit = 0 16 32 = 2 16 i = 2 mod 128 = 2 Ram Block 2 is copied into a line of set, i = 2 32 Miss i = 4 mod 128 = 4 64 = 4 16 Ram Block 4 is copied into a line of set, i = 4 64 Miss i = 8 mod 128 = 8 128 = 8 16 Ram Block 8 is copied into a line of set, i = 8 128 Miss 256 256 i = 16 mod 128 = 16 Mis Ram Block 16 is = 16 16 copied into a line of set, i = 16 512 512 i = 32 mod 128 = 32 Miss Ram Block 32 is = 32 16 copied into a line of set, i = 32 1024 1024 i = 64 mod 128 = 64 Miss Ram Block 64 is = 64 copied into a line of set, i = 64 16 = 125 mod 128 = 125 2014 = 125 16 Ram Block 125 is copied into a line of set, i = 125 2014 Miss i = 0 mod 128 = 0 CPU accesses set, i = 0, and reads the line containing block o Hit = 0 16 i = 0 mod 128 = 0 4 = 0 16 CPU accesses set, i = 0, and reads the line containing block 0 4 Hit i = 2 mod 128 = 2 32 = 2 16 32 Hit CPU accesses set, i = 2, and reads the line containing block 2 If we notice the "Consequence" column, we can see that all of the description indicates either "copied" or "reads". There is no incident of replacement. So, no blocks were replaced. (v) What is the hit ratio? 1 Hit Ratio =- = 12 4 = 33.33% 3 (vi) Show the state of cache memory at the end (the cache lines containing blocks of main memory) RAM Block, i = 0 Set number, i = 0 Set number, i = 1 RAM Block, - 2 Set number,i- 2 Set number, i = 3 RAM Block, j- 4 Set number, i- 4 RAM Block, j-8 Set number, i-8 RAM Block, j- 16 Set number, i- 16 RAM Block, - 32 Set number, i = 32 RAM Block, = 64 Set number, i- 64 RAM Block, 1 = 125 Set number, i- 125 Set number, i- 126 Set number, i- 127

Step by Step Solution

★★★★★

3.50 Rating (147 Votes )

There are 3 Steps involved in it

Step: 1

i Word bits in the address is used to select a particular byte in a cache line 4 bits are used for ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started