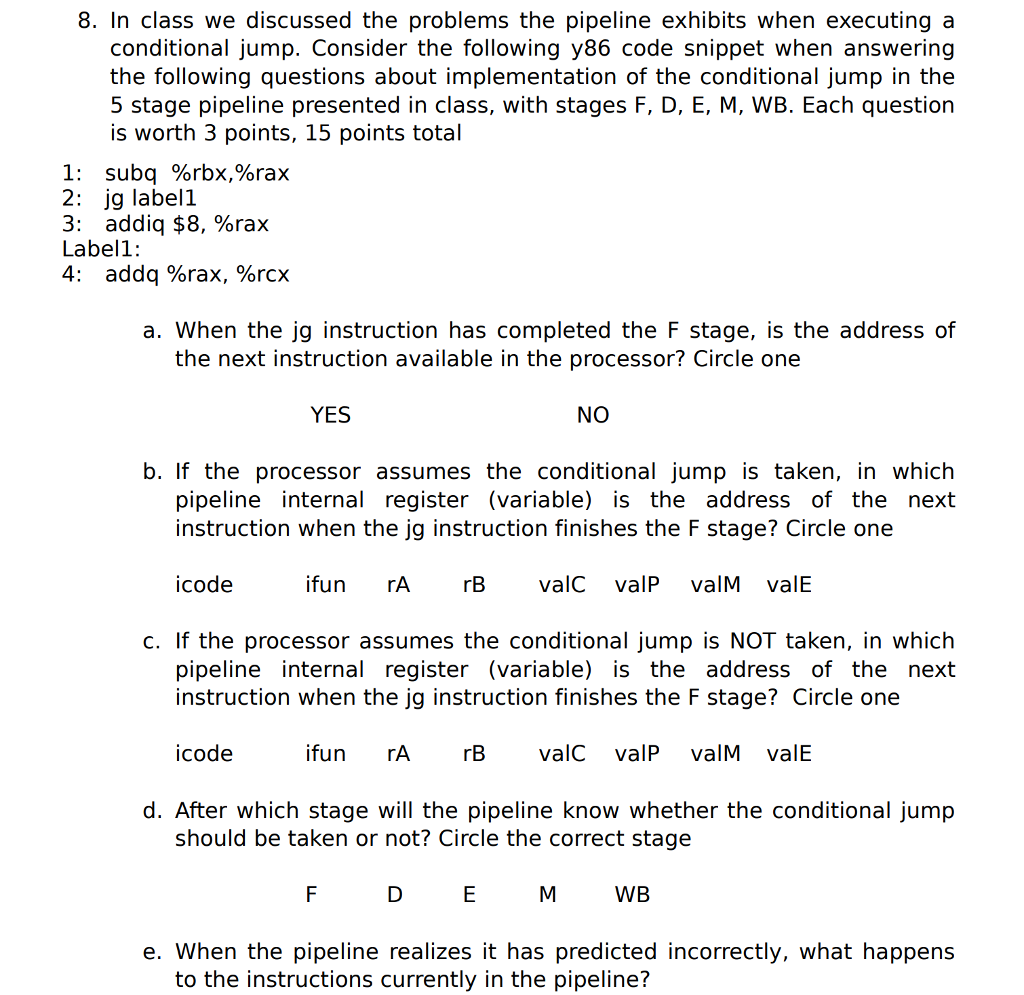

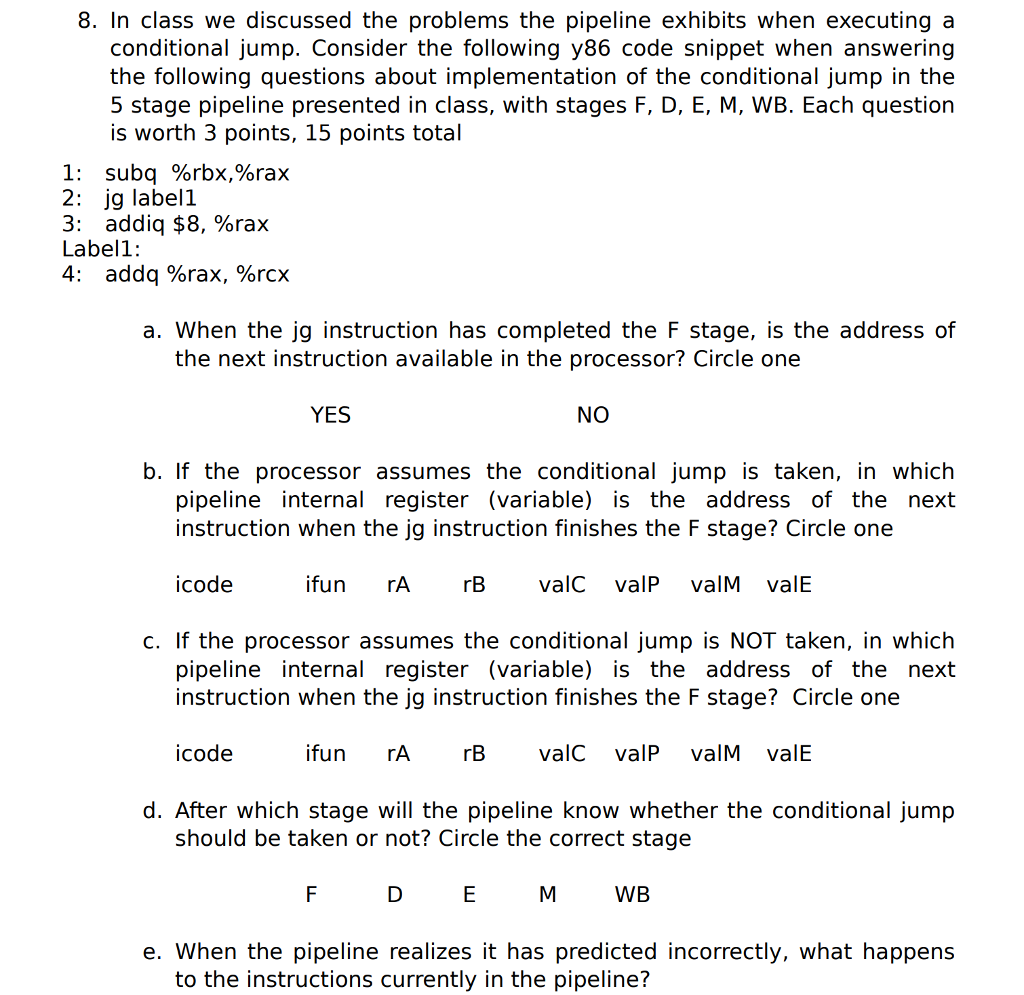

8. In class we discussed the problems the pipeline exhibits when executing a conditional jump. Consider the following y86 code snippet when answering the following questions about implementation of the conditional jump in the 5 stage pipeline presented in class, with stages F, D, E, M, WB. Each question is worth 3 points, 15 points total 1: subq %rbx,%rax 2: jg labell 3: addiq $8,%rax Label1: 4: addq %rax, %rcx a. When the jg instruction has completed the F stage, is the address of the next instruction available in the processor? Circle one YES NO b. If the processor assumes the conditional jump is taken, in which pipeline internal register (variable) is the address of the next instruction when the jg instruction finishes the F stage? Circle one icode ifun rA valC valP valM valE c. If the processor assumes the conditional jump is NOT taken, in which pipeline internal register (variable) is the address of the next instruction when the jg instruction finishes the F stage? Circle one icode ifun rA rB valC valP ValM valE d. After which stage will the pipeline know whether the conditional jump should be taken or not? Circle the correct stage WB e. When the pipeline realizes it has predicted incorrectly, what happens to the instructions currently in the pipeline? 8. In class we discussed the problems the pipeline exhibits when executing a conditional jump. Consider the following y86 code snippet when answering the following questions about implementation of the conditional jump in the 5 stage pipeline presented in class, with stages F, D, E, M, WB. Each question is worth 3 points, 15 points total 1: subq %rbx,%rax 2: jg labell 3: addiq $8,%rax Label1: 4: addq %rax, %rcx a. When the jg instruction has completed the F stage, is the address of the next instruction available in the processor? Circle one YES NO b. If the processor assumes the conditional jump is taken, in which pipeline internal register (variable) is the address of the next instruction when the jg instruction finishes the F stage? Circle one icode ifun rA valC valP valM valE c. If the processor assumes the conditional jump is NOT taken, in which pipeline internal register (variable) is the address of the next instruction when the jg instruction finishes the F stage? Circle one icode ifun rA rB valC valP ValM valE d. After which stage will the pipeline know whether the conditional jump should be taken or not? Circle the correct stage WB e. When the pipeline realizes it has predicted incorrectly, what happens to the instructions currently in the pipeline