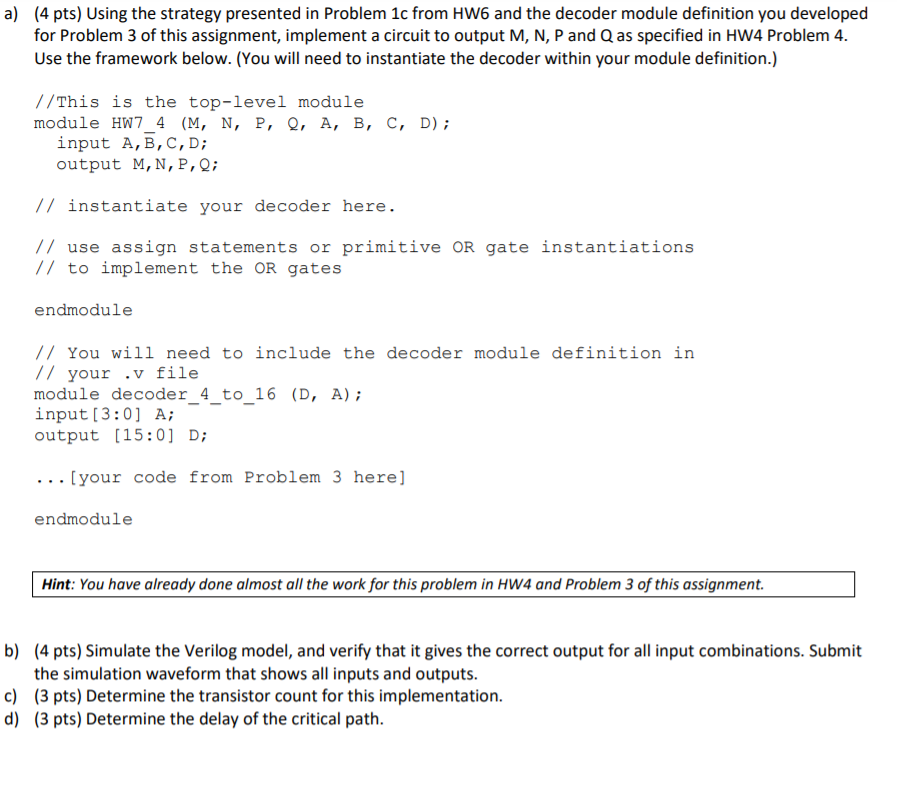

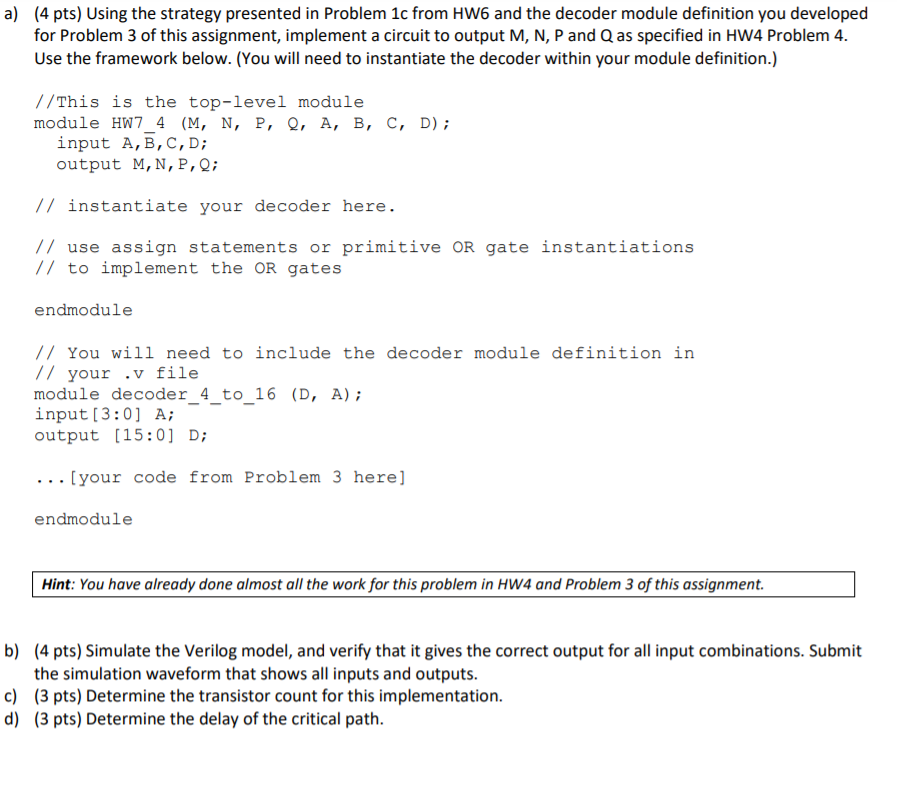

a) (4 pts) Using the strategy presented in Problem 1c from HW6 and the decoder module definition you developed for Problem 3 of this assignment, implement a circuit to output M, N, P and Q as specified in HW4 Problem 4. Use the framework below. (You will need to instantiate the decoder within your module definition.) //This is the top-level module module HW7_4 (M, N, P, Q, A, B, C, D); input A,B,C,D; output M,N,P,Q; // instantiate your decoder here. // use assign statements or primitive OR gate instantiations // to implement the OR gates endmodule // You will need to include the decoder module definition in // your .v file module decoder_4_to_16 (D, A); input [3:0] A; output (15:0] D; ... [your code from Problem 3 here] endmodule Hint: You have already done almost all the work for this problem in HW4 and Problem 3 of this assignment. b) (4 pts) Simulate the Verilog model, and verify that it gives the correct output for all input combinations. Submit the simulation waveform that shows all inputs and outputs. c) (3 pts) Determine the transistor count for this implementation. d) (3 pts) Determine the delay of the critical path. a) (4 pts) Using the strategy presented in Problem 1c from HW6 and the decoder module definition you developed for Problem 3 of this assignment, implement a circuit to output M, N, P and Q as specified in HW4 Problem 4. Use the framework below. (You will need to instantiate the decoder within your module definition.) //This is the top-level module module HW7_4 (M, N, P, Q, A, B, C, D); input A,B,C,D; output M,N,P,Q; // instantiate your decoder here. // use assign statements or primitive OR gate instantiations // to implement the OR gates endmodule // You will need to include the decoder module definition in // your .v file module decoder_4_to_16 (D, A); input [3:0] A; output (15:0] D; ... [your code from Problem 3 here] endmodule Hint: You have already done almost all the work for this problem in HW4 and Problem 3 of this assignment. b) (4 pts) Simulate the Verilog model, and verify that it gives the correct output for all input combinations. Submit the simulation waveform that shows all inputs and outputs. c) (3 pts) Determine the transistor count for this implementation. d) (3 pts) Determine the delay of the critical path