Answered step by step

Verified Expert Solution

Question

1 Approved Answer

A bus is a set of signals which are grouped together conceptually (and often physically). One way to represent a bus is with std_logic_vector,

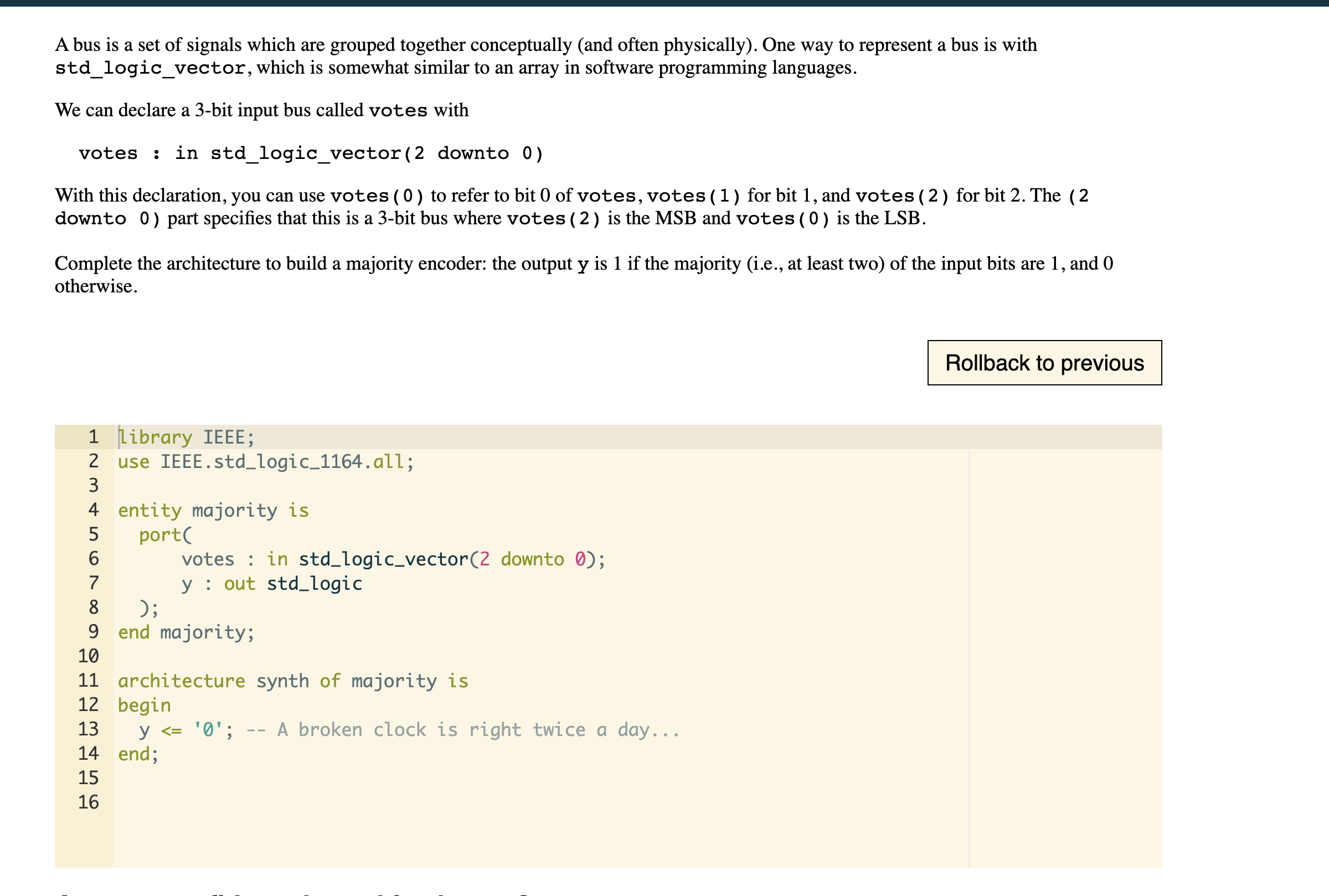

A bus is a set of signals which are grouped together conceptually (and often physically). One way to represent a bus is with std_logic_vector, which is somewhat similar to an array in software programming languages. We can declare a 3-bit input bus called votes with votes : in std_logic_vector (2 downto 0) With this declaration, you can use votes (0) to refer to bit 0 of votes, votes (1) for bit 1, and votes (2) for bit 2. The (2 downto 0) part specifies that this is a 3-bit bus where votes (2) is the MSB and votes (0) is the LSB. Complete the architecture to build a majority encoder: the output y is 1 if the majority (i.e., at least two) of the input bits are 1, and 0 otherwise. 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 4 5 port( 6 7 8 9 10 456 entity majority is 15 11 architecture synth of majority is 12 begin 13 14 16 votes in std_logic_vector(2 downto 0); y out std_logic ); end majority; y

Step by Step Solution

There are 3 Steps involved in it

Step: 1

The image youve shared contains code and a description for a problem where we need to design a ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started