Question: a) Design and draw active-high input SR latch and SR flip flop. Give the truth table. b) Examine the VHDL code of SR Flip

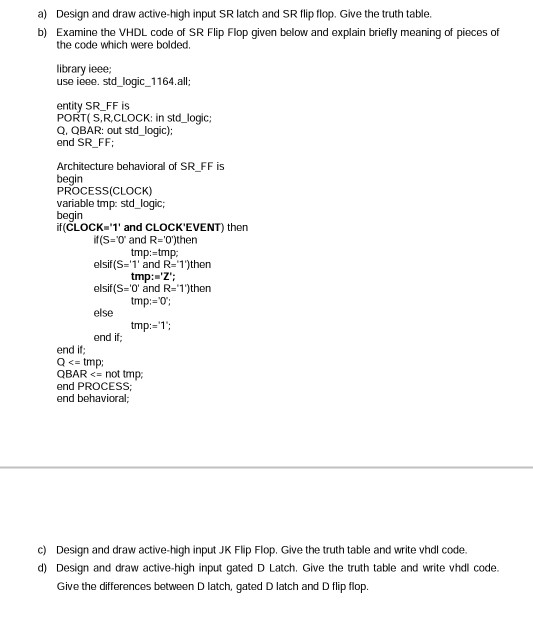

a) Design and draw active-high input SR latch and SR flip flop. Give the truth table. b) Examine the VHDL code of SR Flip Flop given below and explain briefly meaning of pieces of the code which were bolded. library ieee; use ieee. std_logic_1164.all; entity SR_FF is PORT(S.R.CLOCK: in std_logic; Q. QBAR: out std_logic): end SR_FF; Architecture behavioral of SR_FF is begin PROCESS(CLOCK) variable tmp: std_logic; begin if(CLOCK='1' and CLOCK'EVENT) then if(S='0' and R='0')then tmp:=tmp; elsif(S='1' and R='1')then tmp:='Z'; elsif(S='0' and R='1') then tmp:='0'; tmp:='1'; else end if; end if; Q

Step by Step Solution

3.47 Rating (160 Votes )

There are 3 Steps involved in it

a ActiveHigh Input SR Latch Truth table css Copy code S R Q Q 0 0 Q Q Hold 0 1 0 1 Reset 1 0 1 0 Set ... View full answer

Get step-by-step solutions from verified subject matter experts