Answered step by step

Verified Expert Solution

Question

1 Approved Answer

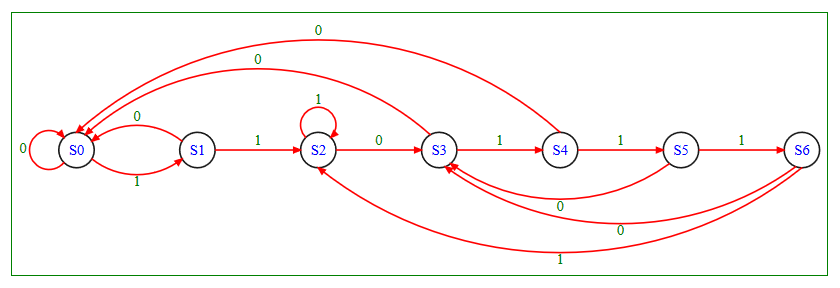

A FSM the recognizes the pattern 110111 is: The states are defined as: typedef enum logic[2:0] {S0, S1, S2, S3, S4, S5, S6} recog_st_t; Any

A FSM the recognizes the pattern 110111 is:

The states are defined as:

typedef enum logic[2:0] {S0, S1, S2, S3, S4, S5, S6} recog_st_t; Any time the pattern is recognized the FSM will enter state S6. The FSM will accept either a 1 or a 0 as input for every clock tick. There are two occurrences of the pattern in the following input:

Complete the recognize module using behavioural Verilog :

module recognize( output recog_st_t state, input logic in, input logic clk, reset );

endmodule

0 SO S1 S2 S3 S4 S5 S6Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started