Question

A given pipelined processor executes floating-point instructions of the type Fi Fj op Fk. It has an I stage (for instruction fetch) and a D

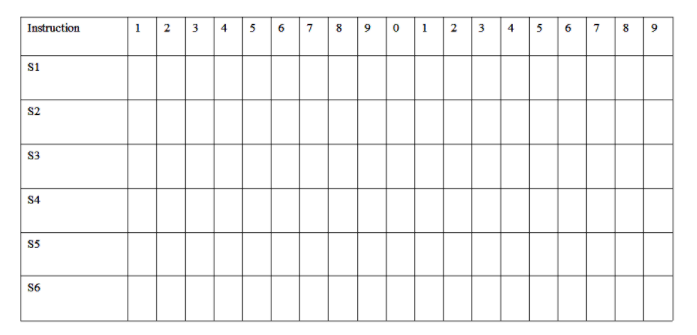

A given pipelined processor executes floating-point instructions of the type Fi Fj op Fk. It has an I stage (for instruction fetch) and a D stage (for instruction decode and operand preparation) each taking one clock cycle. The execution phase of a Floating-point ADD operation and a Floating-point Multiply operation takes 2 and 4 cycles, respectively. Each execution is followed by a single (clock) cycle write back (W) into the floating-point register file which can support simultaneous reads but only a single write per cycle. The processor executes the following sequence of floating-point instructions: S1: F2 F1 + F4 S2: F3 F2 * F4 S3: F3 F4 + F5 S4: F4 F1 * F2 S5: F1 F2 + F3 S6: F4 F1 * F2 Assume that the pipelined processor has a single floating-point adder and a single floating-point multiplier. Also assume that the floating-point adder (with execution time of 2 cycles) and the floating-point multiplier (with execution time of 4 cycles) can operate in parallel and are fully pipelined (with a throughput of 1) Show the exact timing for the above program (on a separate sheet of paper) for the case of the basic pipeline with data forwarding. How many cycles will the above program take to run once? Is it possible to use software scheduling to reduce the number of required cycles? Use the table below for help. (for example, you can not multiply and divide at the same time)

Number of cycles =____?

Is it possible to use software scheduling to reduce the number of required cycles? Yes or No?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started