Question: A) In this part you are asked to recognize what a given segment of machine code does, by translating it into assembly code, and annotating

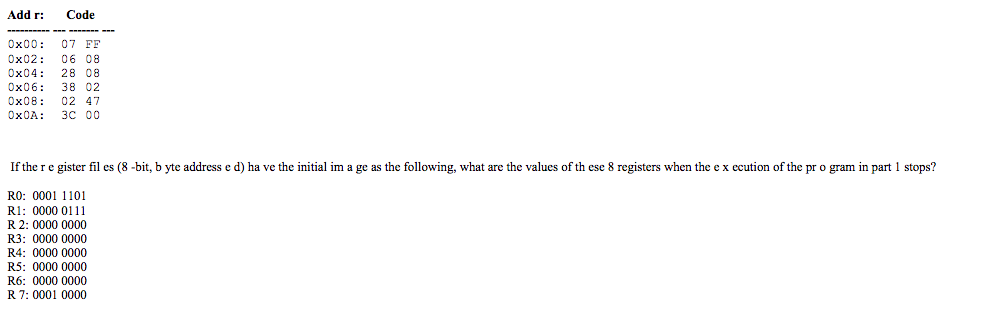

A) In this part you are asked to recognize what a given segment of machine code does, by translating it into assembly code, and annotating it with expressions in a high level language like C. This process, from binary code back to source code, is called disassembling. Disassemble the following machine code into operations and arguments, e. g., ADD R 1, R 2, R 3. Explain what the whole program does, either in plain En glish (e. g., it calculates t he prod uct of R1 and R 2) or in C type of pseudo code (e. g, R3 = R1 * R 2.) Note: you need to make up unique labels for your assembly code.

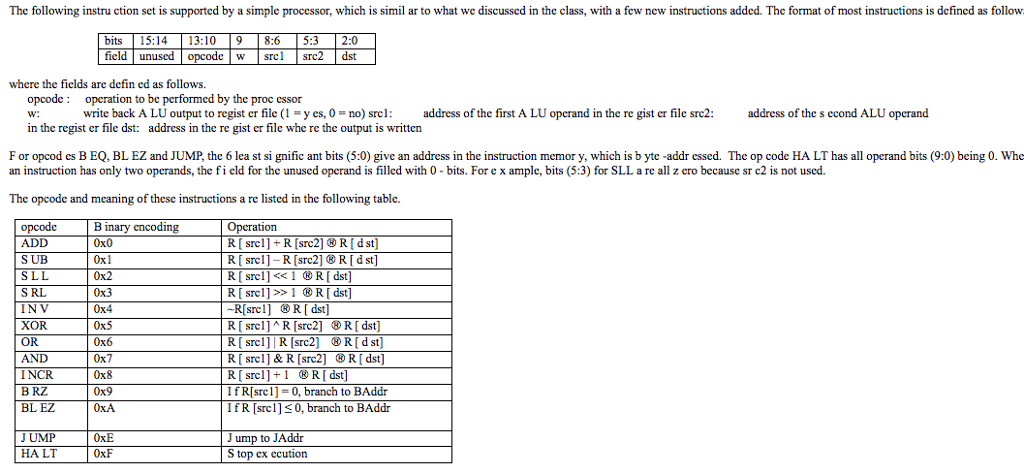

The following instru ction set is supported by asimple processor, which is simil ar to what we discussed in the class, with a few new instructions added. The format of most instructions is defined as follow bits 15:14 13:10 9 8:6 5:3 2:0 field unused opcode w srcl Src2 dst where the fields are defin ed as follows opcode: operation to be performed by the processor write back ALU output to regist er file yes, 0- no) srcl: address of the first ALU operand in the re gist er file src2 address of the second ALU operand in the regist er file dst: address in the re gist er file whe re the output is written For opcod es B EQ, BLEZ and JUMP, the 6 lea st si gnific ant bits (5:0) give an address in the instruction memory, which is b yte -addr esse The op code HA LT has all operand bits (9:0) being 0. Whe an instruction has only two operands, the fi cld for the unused operand is filled with 0-bits. For example, bits (5:3) for SLL a re allzero because s c2 is not used. The opcode and meaning of these instructions a re listed in the following table. Binary encoding opcode Operation ADD SUB SLL 0x2 SRL R. srcij 1 BR [dst] INV OR INCR CX8 RI Srl +1 dist BRZ I fRIsrclj 0, branch to BAddr BLEZ 0xAA If R [srcijs 0, branch to BAddr Jump to JAddr JUMP 0xE GXF S top execution HALT The following instru ction set is supported by asimple processor, which is simil ar to what we discussed in the class, with a few new instructions added. The format of most instructions is defined as follow bits 15:14 13:10 9 8:6 5:3 2:0 field unused opcode w srcl Src2 dst where the fields are defin ed as follows opcode: operation to be performed by the processor write back ALU output to regist er file yes, 0- no) srcl: address of the first ALU operand in the re gist er file src2 address of the second ALU operand in the regist er file dst: address in the re gist er file whe re the output is written For opcod es B EQ, BLEZ and JUMP, the 6 lea st si gnific ant bits (5:0) give an address in the instruction memory, which is b yte -addr esse The op code HA LT has all operand bits (9:0) being 0. Whe an instruction has only two operands, the fi cld for the unused operand is filled with 0-bits. For example, bits (5:3) for SLL a re allzero because s c2 is not used. The opcode and meaning of these instructions a re listed in the following table. Binary encoding opcode Operation ADD SUB SLL 0x2 SRL R. srcij 1 BR [dst] INV OR INCR CX8 RI Srl +1 dist BRZ I fRIsrclj 0, branch to BAddr BLEZ 0xAA If R [srcijs 0, branch to BAddr Jump to JAddr JUMP 0xE GXF S top execution HALT

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts