Answered step by step

Verified Expert Solution

Question

1 Approved Answer

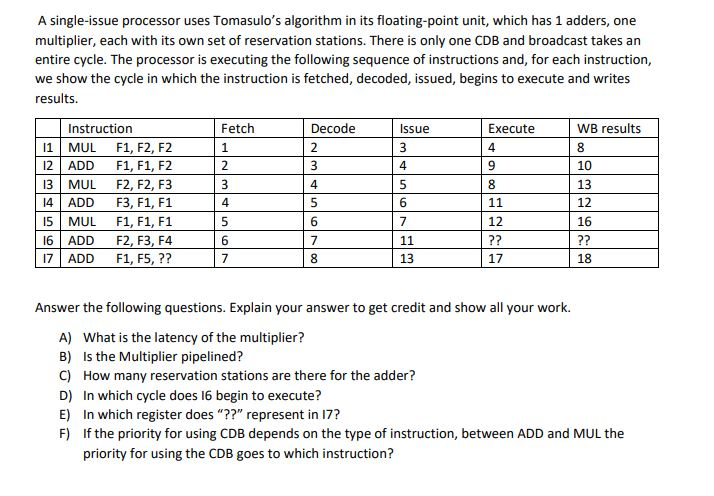

A single-issue processor uses Tomasulo's algorithm in its floating-point unit, which has 1 adders, one multiplier, each with its own set of reservation stations. There

A single-issue processor uses Tomasulo's algorithm in its floating-point unit, which has 1 adders, one multiplier, each with its own set of reservation stations. There is only one CDB and broadcast takes an entire cycle. The processor is executing the following sequence of instructions and, for each instruction, we show the cycle in which the instruction is fetched, decoded, issued, begins to execute and writes results. Fetch Decode WB results Instruction 11 MUL F1, F2, F2 2 ADD F1, F1, F2 13 MUL F2, F2, F3 4 ADD F3, F1, F1 15|MUL Fl,F1, F1 6 ADD F2, F3, F4 7 ADD F1, F5, ?? Issue Execute 4 13 12 4 12 13 17 18 Answer the following questions. Explain your answer to get credit and show all your work. A) What is the latency of the multiplier? B) Is the Multiplier pipelined? C) How many reservation stations are there for the adder? D) In which cycle does 16 begin to execute? E) In which register does"??" represent in 17? F) If the priority for using CDB depends on the type of instruction, between ADD and MUL the priority for using the CDB goes to which instruction

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started