Question

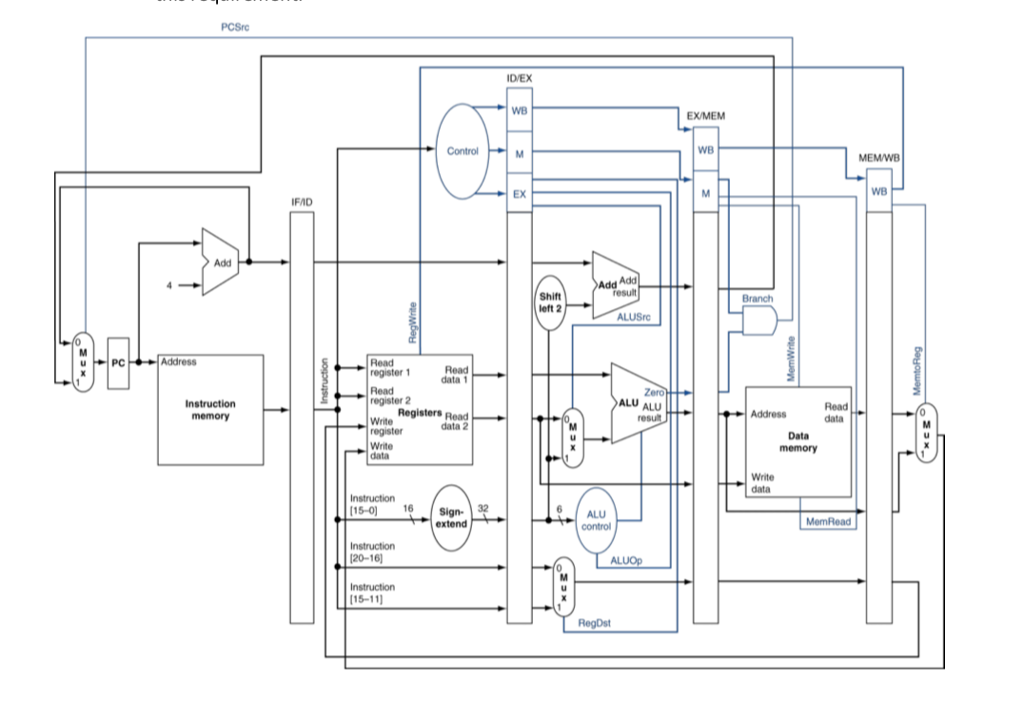

Answer the following questions based on the image shown below; a) A 5-stage MIPS pipeline design is shown below. Highlight the EX and the MEM

Answer the following questions based on the image shown below;

Answer the following questions based on the image shown below;

a) A 5-stage MIPS pipeline design is shown below. Highlight the EX and the MEM stages of the data path and control signals needed for executing beq instruction in this 5-stage MIPS pipeline. Note, you can circle the needed components and draw (bold) the line for the wires connecting these components.

b) In this design, how many stall cycles caused by beq without using any branch prediction mechanism (i.e. stalls are always inserted)?

c) You want to reduce one stall cycle without moving branch condition evaluation and target address calculation away from the EX stage. Describe qualitatively how you can accomplish this requirement.

PCSrc IDVEX WB EX/MEM WB EX WB FAD Add Shift left 2 ALUSre register 1 data 1 register 2 ALU Registers Read data 2 Data 115-01 / Sign- ) 32 6 ALU 20-16 15-11

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started