Answered step by step

Verified Expert Solution

Question

1 Approved Answer

ASAP PLEASE Question 2 (a) Consider a basic pipeline with 5 stages: Fetch Instruction (FI), Decode Instruction (DI). Read Operand (RO), Execute Instruction (EI) and

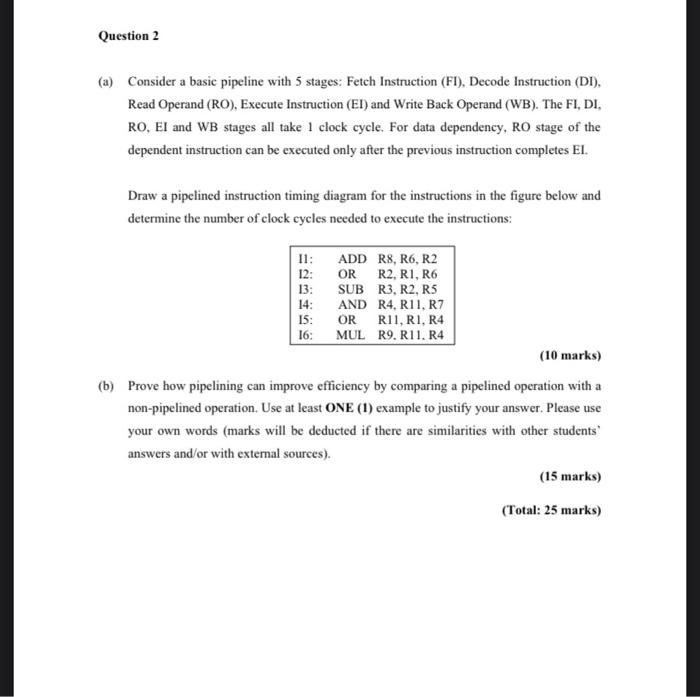

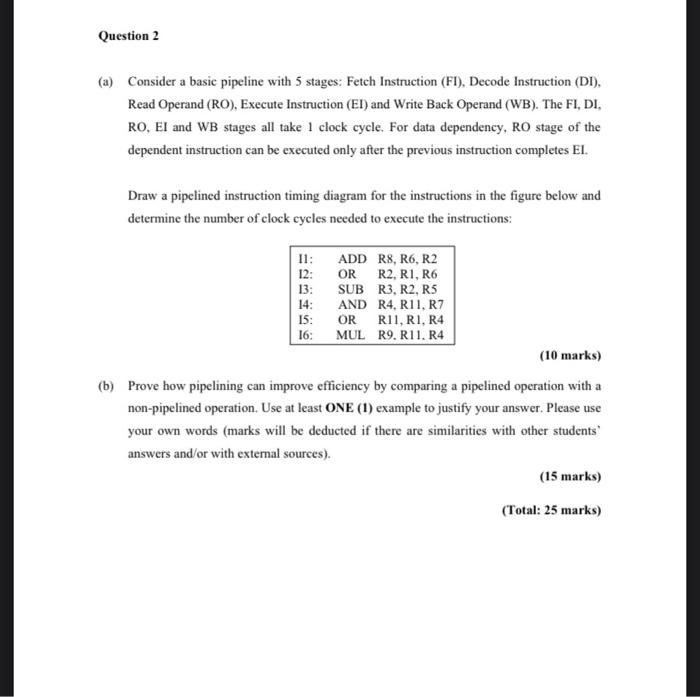

ASAP PLEASE  Question 2 (a) Consider a basic pipeline with 5 stages: Fetch Instruction (FI), Decode Instruction (DI). Read Operand (RO), Execute Instruction (EI) and Write Back Operand (WB). The FI, DI, RO, El and WB stages all take 1 clock cycle. For data dependency, RO stage of the dependent instruction can be executed only after the previous instruction completes El. Draw a pipelined instruction timing diagram for the instructions in the figure below and determine the number of clock cycles needed to execute the instructions: 11: 12: 13: 14: 15: 16: ADD R8, R6, R2 OR R2, R1, R6 SUB R3, R2, RS AND R4, R11, R7 OR RII, RI, R4 MUL R9, R11, R4 (10 marks) (b) Prove how pipelining can improve efficiency by comparing a pipelined operation with a non-pipelined operation. Use at least ONE (1) example to justify your answer. Please use your own words (marks will be deducted if there are similarities with other students' answers and/or with external sources). (15 marks) (Total: 25 marks)

Question 2 (a) Consider a basic pipeline with 5 stages: Fetch Instruction (FI), Decode Instruction (DI). Read Operand (RO), Execute Instruction (EI) and Write Back Operand (WB). The FI, DI, RO, El and WB stages all take 1 clock cycle. For data dependency, RO stage of the dependent instruction can be executed only after the previous instruction completes El. Draw a pipelined instruction timing diagram for the instructions in the figure below and determine the number of clock cycles needed to execute the instructions: 11: 12: 13: 14: 15: 16: ADD R8, R6, R2 OR R2, R1, R6 SUB R3, R2, RS AND R4, R11, R7 OR RII, RI, R4 MUL R9, R11, R4 (10 marks) (b) Prove how pipelining can improve efficiency by comparing a pipelined operation with a non-pipelined operation. Use at least ONE (1) example to justify your answer. Please use your own words (marks will be deducted if there are similarities with other students' answers and/or with external sources). (15 marks) (Total: 25 marks)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started