Answered step by step

Verified Expert Solution

Question

1 Approved Answer

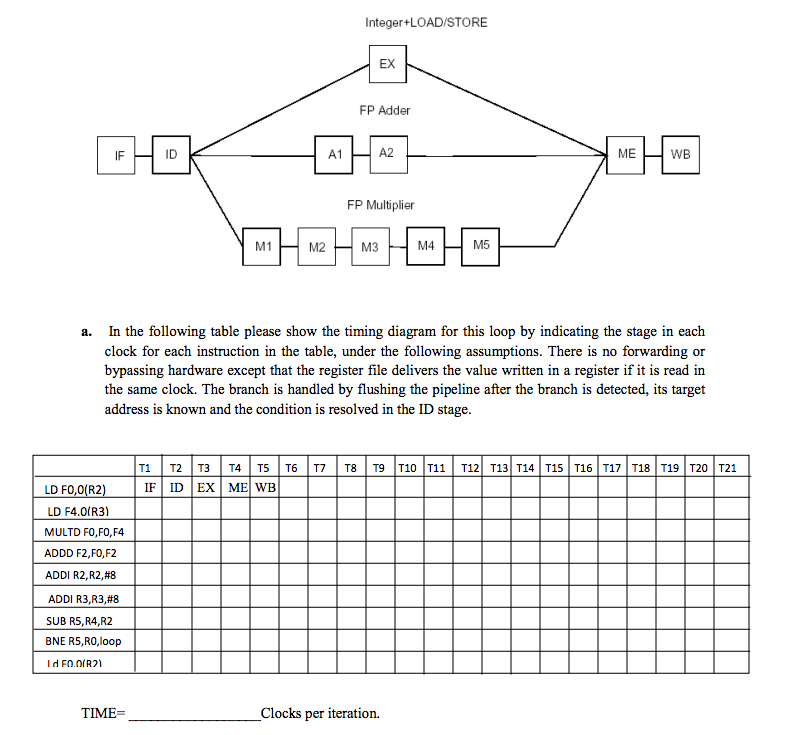

Assume a floating point pipeline with multiple execution units as shown in the following Figure. The address (integer) unit takes one clock. The FP adder

Assume a floating point pipeline with multiple execution units as shown in the following Figure. The address (integer) unit takes one clock. The FP adder and FP multiplier are fully pipelined and take 2 and 5 clocks respectively. If structural hazards are due to write-back contention, assume that the earliest instruction gets priority and other instructions are stalled.

Consider the following program:

LOOP LD F0,0(R2)

LD F4,0(R3)

MULTD F0,F0,F4

ADDD F2,F0,F2

ADDI R2,R2,#8

ADDI R3,R3,#8

SUB R5,R4,R2

BNE R5,R0,LOOP

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started