Question

Assume that a computer is to run the following three instructions (below) on a Floating-Point pipeline as described in MyCh07e lecture. This Floating-Point pipeline will

Assume that a computer is to run the following three instructions (below) on a Floating-Point pipeline as described in MyCh07e lecture. This Floating-Point pipeline will have the same Floating-Point Functional Units as depicted on Slide 5 in MyCh07e. ADD F1, F2, F3

ADD F4, F1, F5

MUL F5, F4, F6 a) How many clock cycles would it take to execute all three of these instructions if they were NOT pipelined?

b) How many clock cycles would it take to execute all three of these instructions if they were pipelined but there was NO data forwarding?

c) How many clock cycles would it take to execute all three of these instructions if they were pipelined AND data forwarding were allowed?

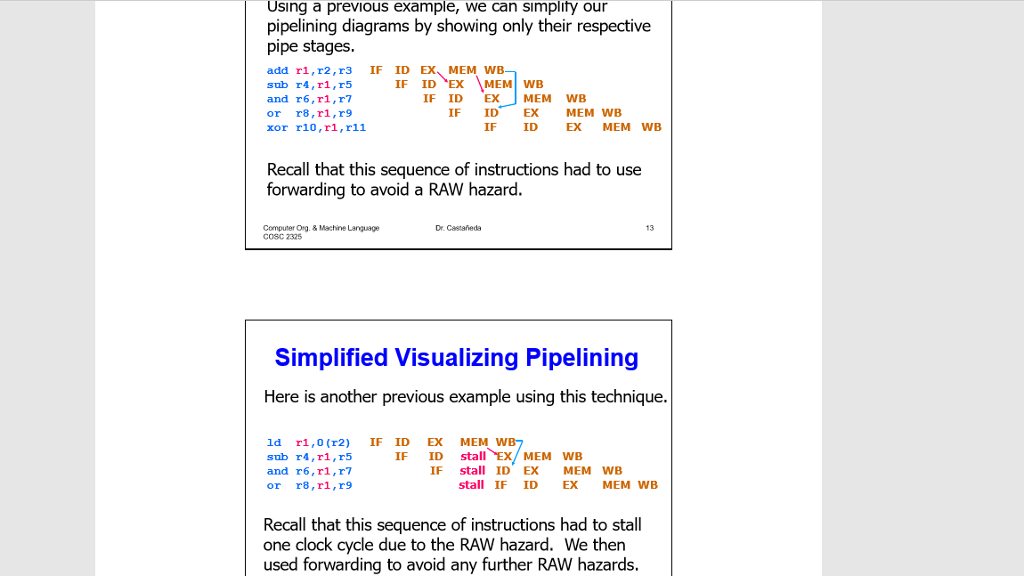

Draw out how the pipeline flow would look like when these instructions are executed. If applicable, show any stalls with an s or the word stall. Also show/annotate/write where there would be any data forwarding. Show if there are any times when writing to the register file and reading from the register file occur at the same clock cycle. Note: recall that writing to a register file occurs in the first half of a clock cycle while reading from a register file occurs in the second half of a clock cycle. You may use an arrow to show this or simply write down where the data forwarding would occur but you must be accurate so that there is no ambiguity in your answer. Look at my lecture slides in MyCh07d for examples. But specifically, I expect your answer to look something like what is on my slides 13 or 14 in MyCh07d. Also, you may use the following abbreviations in your pipeline: F instruction fetch

D decode

A1 A2 A3 A4 Add FP

M1 M2 M3 M4 M5 M6 M7 Mult FP

MM memory

W write back

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started