Answered step by step

Verified Expert Solution

Question

1 Approved Answer

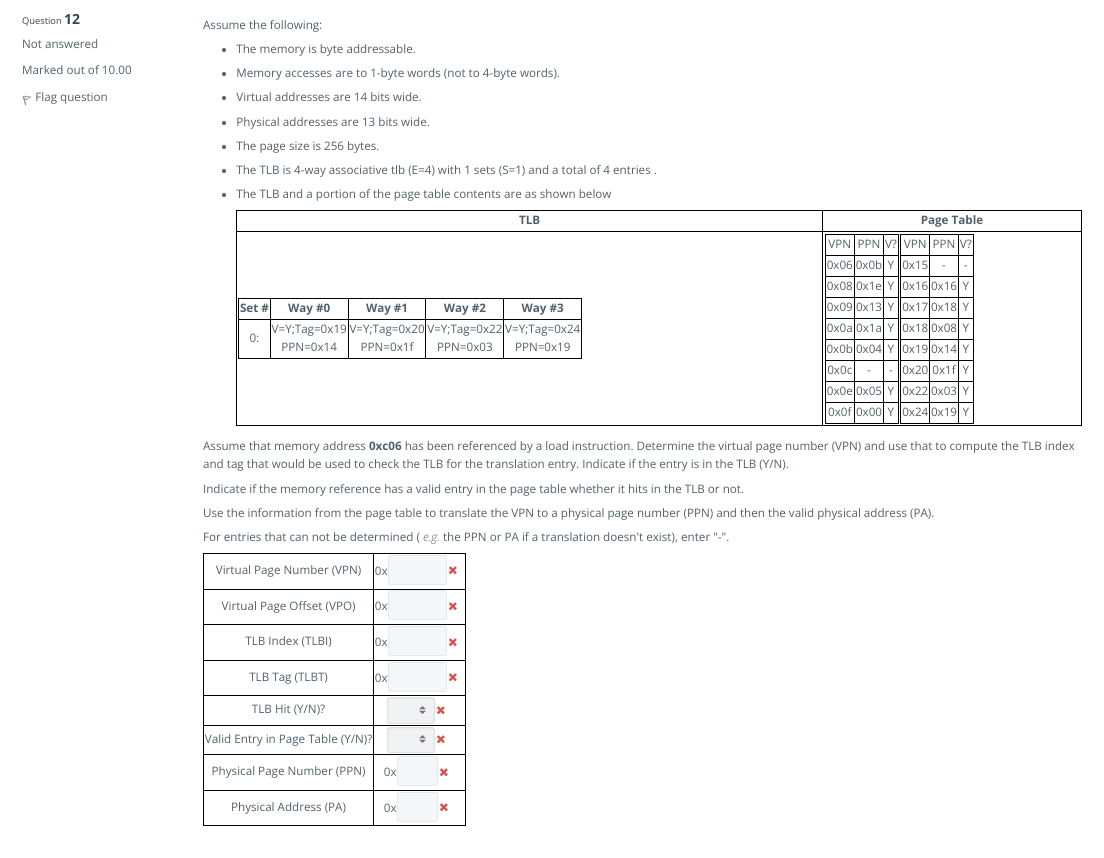

Assume the following: The memory is byte addressable. Memory accesses are to 1 - byte words ( not to 4 - byte words ) .

Assume the following:

The memory is byte addressable.

Memory accesses are to byte words not to byte words

Virtual addresses are bits wide.

Physical addresses are bits wide.

The page size is bytes.

The TLB is way associative tlb with sets and a total of entries

The TLB and a portion of the page table contents are as shown below

Assume that memory address xc has been referenced by a load instruction. Determine the virtual page number VPN and use that to compute the TLB index

and tag that would be used to check the TLB for the translation entry. Indicate if the entry is in the TLB YN

Indicate if the memory reference has a valid entry in the page table whether it hits in the TLB or not.

Use the information from the page table to translate the VPN to a physical page number PPN and then the valid physical address PA

For entries that can not be determined eg the PPN or PA if a translation doesn't exist enter

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started