Answered step by step

Verified Expert Solution

Question

1 Approved Answer

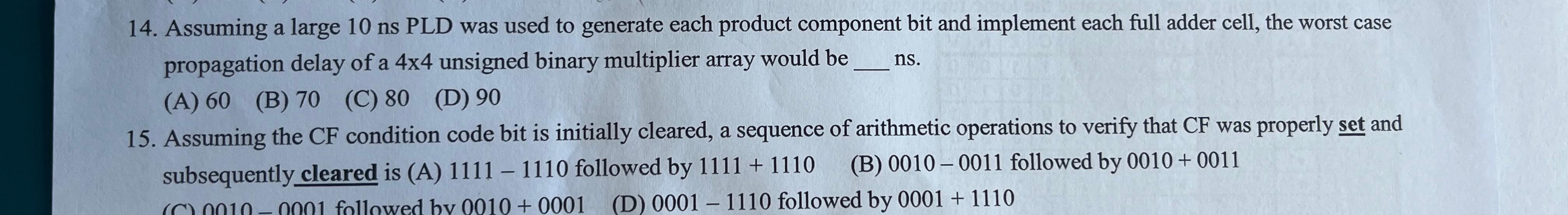

Assuming a large 1 0 n s PLD was used to generate each product component bit and implement each full adder cell, the worst case

Assuming a large PLD was used to generate each product component bit and implement each full adder cell, the worst case propagation delay of a unsigned binary multiplier array would be ns

A

B

C

D

Assuming the CF condition code bit is initially cleared, a sequence of arithmetic operations to verify that CF was properly set and subsequently cleared is A followed by

B followed by

D followed by

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started