Answered step by step

Verified Expert Solution

Question

1 Approved Answer

b . In the full adder circuit shown below, all gates are assumed to have the same gate - delay D . Figure 5 b:

b In the full adder circuit shown below, all gates are assumed to have the

same gatedelay D

Figure b: Full adder circuit

i Write the Boolean expression of:

and in terms of and

in terms of and and

in terms of and

How long is the longest propagation delay

from and to

from and to and

from to

marks

ii A bit ripple carry adder is realized using full adders shown in

Figure with What is the worstcase delay in number of

gatedelay D for this bit adder? Explain your calculation clearly.

marks

iii. Compare the advantages and disadvantages of asynchronous ripple

carry adder and Carry Look ahead adder?

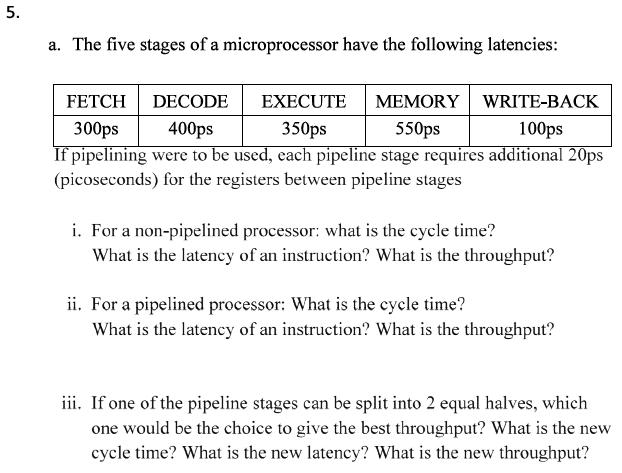

a The five stages of a microprocessor have the following latencies:

If pipelining were to be used, each pipeline stage requires additional ps

picoseconds for the registers between pipeline stages

i For a nonpipelined processor: what is the cycle time?

What is the latency of an instruction? What is the throughput?

ii For a pipelined processor: What is the cycle time?

What is the latency of an instruction? What is the throughput?

iii. If one of the pipeline stages can be split into equal halves, which

one would be the choice to give the best throughput? What is the new

cycle time? What is the new latency? What is the new throughput?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started