Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Based on the solution provided, solve the rest of the questions please ASAP, I need it quicklyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyy Q1: A gaming device has to transfer a

Based on the solution provided, solve the rest of the questions please ASAP, I need it quicklyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyy

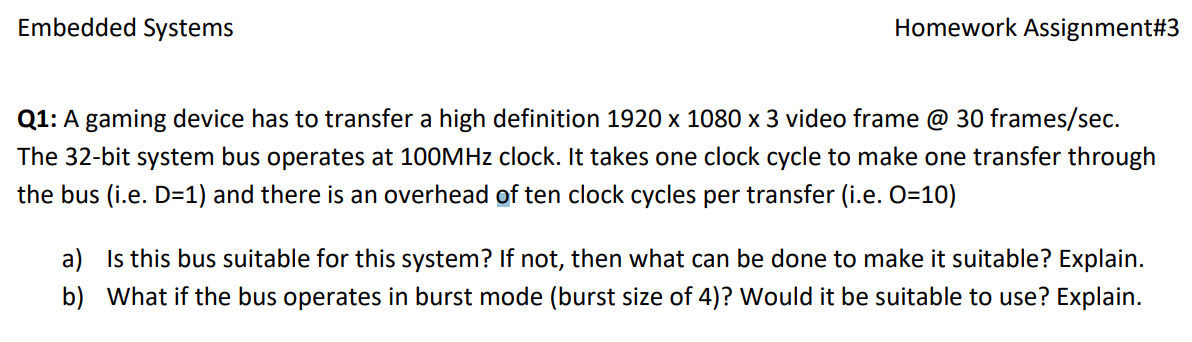

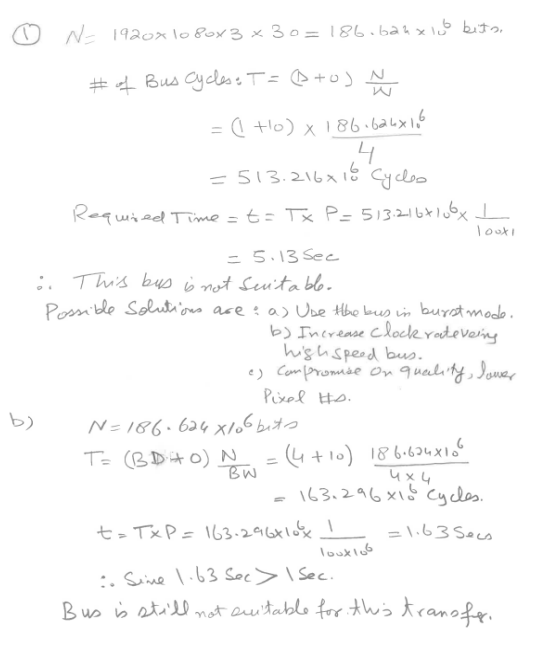

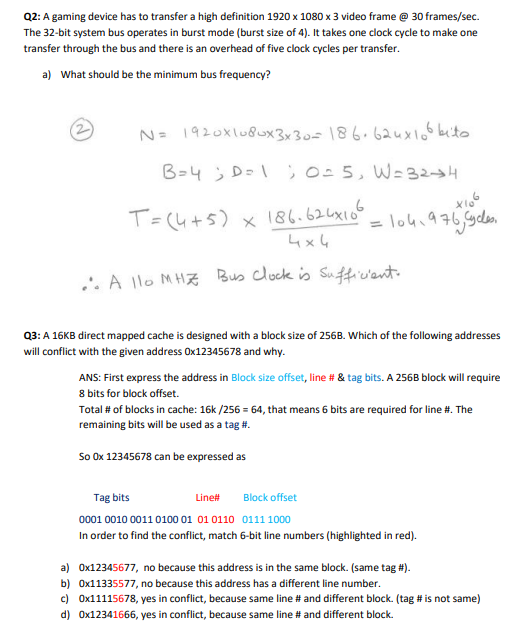

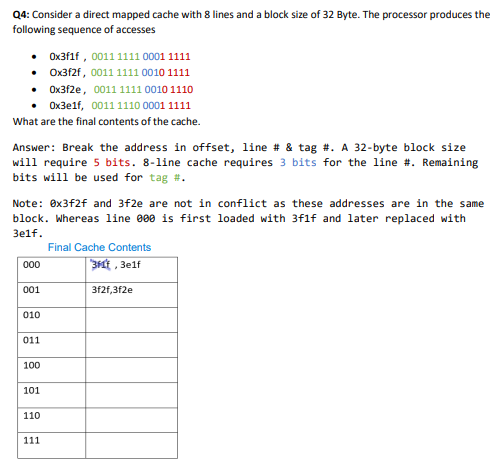

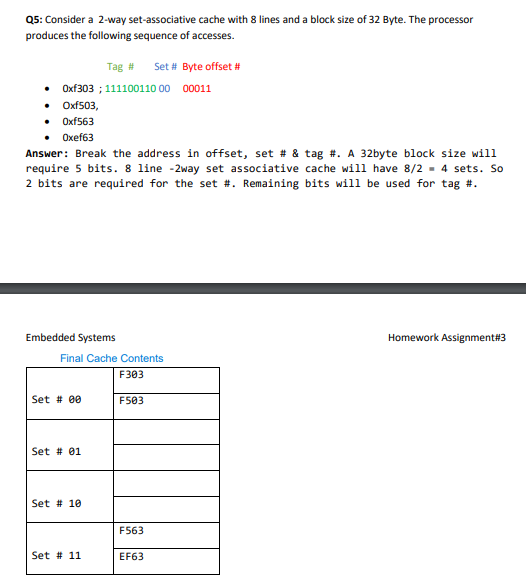

Q1: A gaming device has to transfer a high definition 1920 x 1080 x 3 video frame @ 30 frames/sec. The 32 -bit system bus operates at 100MHz clock. It takes one clock cycle to make one transfer through the bus (i.e. D=1 ) and there is an overhead of ten clock cycles per transfer (i.e. 0=10 ) a) Is this bus suitable for this system? If not, then what can be done to make it suitable? Explain. b) What if the bus operates in burst mode (burst size of 4)? Would it be suitable to use? Explain. (1) N=19201080330=186.624106bits.#ofBusCycles:T=(B+0)WN=(1+10)4186.626106=513.216106CyclosRequiedTime=t=TxP=513.21610610011=5.13sec This bus in not sinitable. Possible Solutions are: a) Use the bus in burst mode. b) Increase Clock rateveing high speed bus. e) Compromide on quality, lower Pixpl \#s. b) N=186.624106bitsT=(BD+0)BWN=(4+10)44186.624106=163.296106cycles.t=TP=163.2961061001061=1.63secSine1.63sec>1sec. Bus is still not euritable for this transfer. Q2: A gaming device has to transfer a high definition 192010803 video frame @ 30 frames/sec. The 32-bit system bus operates in burst mode (burst size of 4). It takes one clock cycle to make one transfer through the bus and there is an overhead of five clock cycles per transfer. a) What should be the minimum bus frequency? (2) N=19201080330=186.624106bitoB=4;D=1;O=5,W=324T=(4+5)44186.624106=104.976,0.9yes.A110MHZBusClockisSufficient. Q3: A 16KB direct mapped cache is designed with a block size of 256B. Which of the following addresses will conflict with the given address 012345678 and why. ANS: First express the address in Block size offset, line \# \& tag bits. A 256 B block will require 8 bits for block offset. Total \# of blocks in cache: 16k/256=64, that means 6 bits are required for line \#. The remaining bits will be used as a tag \#. So 012345678 can be expressed as Tag bits Line\# 00010010001101000101011001111000 In order to find the conflict, match 6-bit line numbers (highlighted in red). a) 0x12345677, no because this address is in the same block. (same tag \#). b) 0x11335577, no because this address has a different line number. c) Ox11115678, yes in conflict, because same line \# and different block. (tag \# is not same) d) 0x12341666, yes in conflict, because same line \# and different block. Q4: Consider a direct mapped cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses - 0x3f1f, 0011111100011111 - Ox3f2f, 0011111100101111 - Ox3f2e, 0011111100101110 - 0x3e1f, 0011111000011111 What are the final contents of the cache. Answer: Break the address in offset, line \# \& tag \#. A 32-byte block size will require 5 bits. 8 -line cache requires 3 bits for the line \#. Remaining bits will be used for tag \#. Note: 03f2f and 3f2e are not in conflict as these addresses are in the same block. Whereas line 000 is first loaded with 3f1f and later replaced with 3e1f. Q5: Consider a 2-way set-associative cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses. Tag \# Set \# Byte offset \# - 0xf303;1111001100000011 - Oxf503, - 0xf563 - 0xef63 Answer: Break the address in offset, set \# \& tag \#. A 32 byte block size will require 5 bits. 8 line -2 way set associative cache will have 8/2=4 sets. So 2 bits are required for the set \#. Remaining bits will be used for tag \#. Embedded Systems Homework Assignment\#3

Q1: A gaming device has to transfer a high definition 1920 x 1080 x 3 video frame @ 30 frames/sec. The 32 -bit system bus operates at 100MHz clock. It takes one clock cycle to make one transfer through the bus (i.e. D=1 ) and there is an overhead of ten clock cycles per transfer (i.e. 0=10 ) a) Is this bus suitable for this system? If not, then what can be done to make it suitable? Explain. b) What if the bus operates in burst mode (burst size of 4)? Would it be suitable to use? Explain. (1) N=19201080330=186.624106bits.#ofBusCycles:T=(B+0)WN=(1+10)4186.626106=513.216106CyclosRequiedTime=t=TxP=513.21610610011=5.13sec This bus in not sinitable. Possible Solutions are: a) Use the bus in burst mode. b) Increase Clock rateveing high speed bus. e) Compromide on quality, lower Pixpl \#s. b) N=186.624106bitsT=(BD+0)BWN=(4+10)44186.624106=163.296106cycles.t=TP=163.2961061001061=1.63secSine1.63sec>1sec. Bus is still not euritable for this transfer. Q2: A gaming device has to transfer a high definition 192010803 video frame @ 30 frames/sec. The 32-bit system bus operates in burst mode (burst size of 4). It takes one clock cycle to make one transfer through the bus and there is an overhead of five clock cycles per transfer. a) What should be the minimum bus frequency? (2) N=19201080330=186.624106bitoB=4;D=1;O=5,W=324T=(4+5)44186.624106=104.976,0.9yes.A110MHZBusClockisSufficient. Q3: A 16KB direct mapped cache is designed with a block size of 256B. Which of the following addresses will conflict with the given address 012345678 and why. ANS: First express the address in Block size offset, line \# \& tag bits. A 256 B block will require 8 bits for block offset. Total \# of blocks in cache: 16k/256=64, that means 6 bits are required for line \#. The remaining bits will be used as a tag \#. So 012345678 can be expressed as Tag bits Line\# 00010010001101000101011001111000 In order to find the conflict, match 6-bit line numbers (highlighted in red). a) 0x12345677, no because this address is in the same block. (same tag \#). b) 0x11335577, no because this address has a different line number. c) Ox11115678, yes in conflict, because same line \# and different block. (tag \# is not same) d) 0x12341666, yes in conflict, because same line \# and different block. Q4: Consider a direct mapped cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses - 0x3f1f, 0011111100011111 - Ox3f2f, 0011111100101111 - Ox3f2e, 0011111100101110 - 0x3e1f, 0011111000011111 What are the final contents of the cache. Answer: Break the address in offset, line \# \& tag \#. A 32-byte block size will require 5 bits. 8 -line cache requires 3 bits for the line \#. Remaining bits will be used for tag \#. Note: 03f2f and 3f2e are not in conflict as these addresses are in the same block. Whereas line 000 is first loaded with 3f1f and later replaced with 3e1f. Q5: Consider a 2-way set-associative cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses. Tag \# Set \# Byte offset \# - 0xf303;1111001100000011 - Oxf503, - 0xf563 - 0xef63 Answer: Break the address in offset, set \# \& tag \#. A 32 byte block size will require 5 bits. 8 line -2 way set associative cache will have 8/2=4 sets. So 2 bits are required for the set \#. Remaining bits will be used for tag \#. Embedded Systems Homework Assignment\#3 Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started