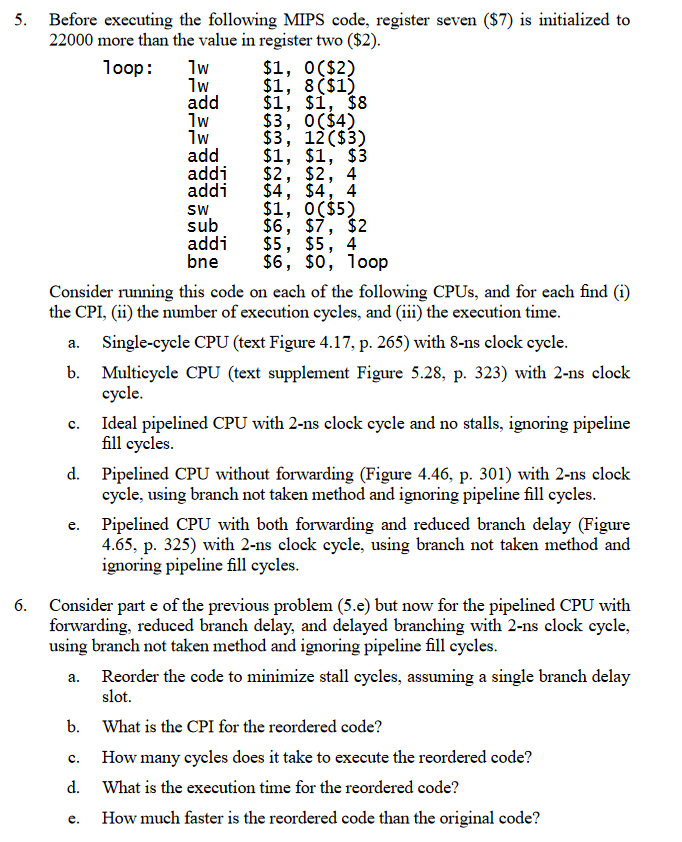

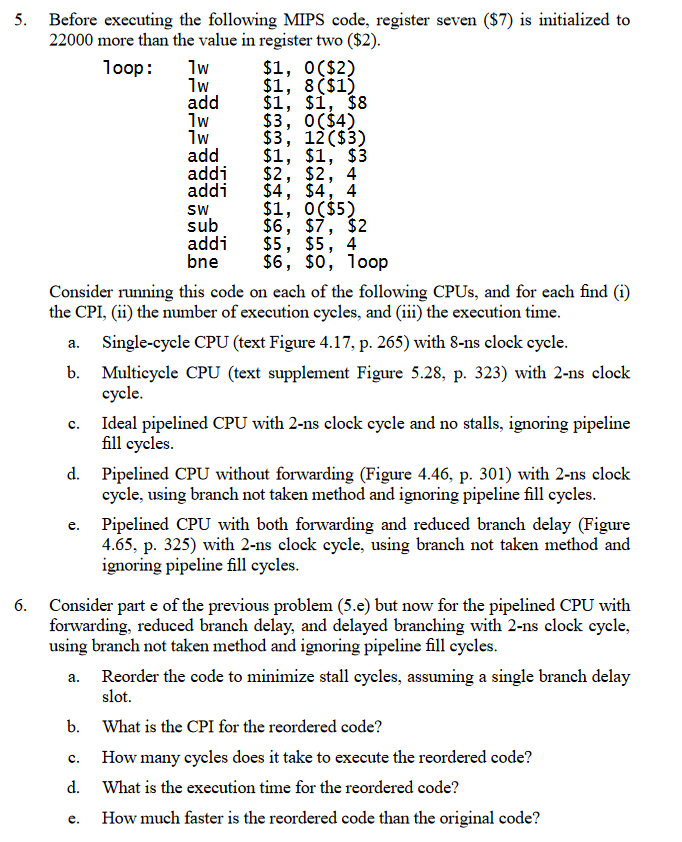

Before executing the following MIPS code, register seven ($7) is initialized to 22000 more than the value in register two ($2) 5. loop 1w $1, 0(S2) $1, 8(S1) $1, $1, $8 $3, O(S4) $3, 12($3) add add$1, $1, $3 addi $2, $2, 4 addi $4, $4, 4 SW sub addi $5, $5, 4 $1, o(S5) $6, $7, $2 Consider running this code on each of the following CPUs, and for each find (i) the CPI, (ii) the number of execution cycles, and (iii) the execution time Single-cycle CPU (text Figure 4.17, p. 265) with 8-ns clock cycle Multicycle CPU (text supplement Figure 5.28, p. 323) with 2-ns clock cycle Ideal pipelined CPU with 2-ns clock cycle and no stalls, ignoring pipeline fill cycles a. b. c. d. Pipelined CPU without forwarding (Figure 4.46, p. 301) with 2-ns clock cycle, using branch not taken method and ignoring Pipelined CPU with both forwarding and reduced branch delay (Figure 4.65, p. 325) with 2-ns clock cycle, using branch not taken method and ignoring pipeline fill cycles pipeline fill cycles e. 6. Consider part e of the previous problem (5.e) but now for the pipelined CPU with forwarding, reduced branch delay, and delayed branching with 2-ns clock cycle, using branch not taken method and ignoring pipeline fill cycles Reorder the code to minimize stall cycles, assuming a single branch delay a. slot. b. What is the CPI for the reordered code? c. How many cycles does it take to execute the reordered code? d. What is the execution time for the reordered code? e. How much faster is the reordered code than the original code? Before executing the following MIPS code, register seven ($7) is initialized to 22000 more than the value in register two ($2) 5. loop 1w $1, 0(S2) $1, 8(S1) $1, $1, $8 $3, O(S4) $3, 12($3) add add$1, $1, $3 addi $2, $2, 4 addi $4, $4, 4 SW sub addi $5, $5, 4 $1, o(S5) $6, $7, $2 Consider running this code on each of the following CPUs, and for each find (i) the CPI, (ii) the number of execution cycles, and (iii) the execution time Single-cycle CPU (text Figure 4.17, p. 265) with 8-ns clock cycle Multicycle CPU (text supplement Figure 5.28, p. 323) with 2-ns clock cycle Ideal pipelined CPU with 2-ns clock cycle and no stalls, ignoring pipeline fill cycles a. b. c. d. Pipelined CPU without forwarding (Figure 4.46, p. 301) with 2-ns clock cycle, using branch not taken method and ignoring Pipelined CPU with both forwarding and reduced branch delay (Figure 4.65, p. 325) with 2-ns clock cycle, using branch not taken method and ignoring pipeline fill cycles pipeline fill cycles e. 6. Consider part e of the previous problem (5.e) but now for the pipelined CPU with forwarding, reduced branch delay, and delayed branching with 2-ns clock cycle, using branch not taken method and ignoring pipeline fill cycles Reorder the code to minimize stall cycles, assuming a single branch delay a. slot. b. What is the CPI for the reordered code? c. How many cycles does it take to execute the reordered code? d. What is the execution time for the reordered code? e. How much faster is the reordered code than the original code