Question

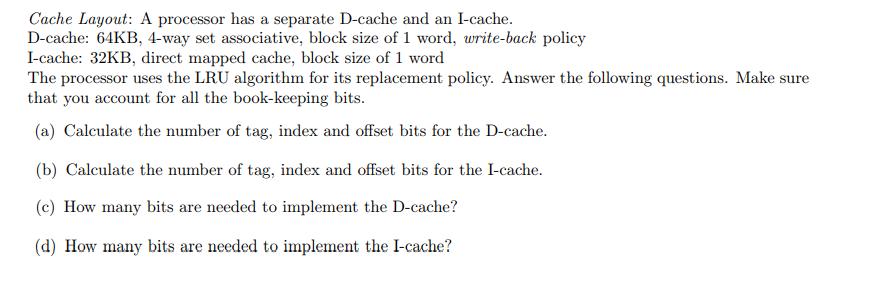

Cache Layout: A processor has a separate D-cache and an I-cache. D-cache: 64KB, 4-way set associative, block size of 1 word, write-back policy I-cache:

Cache Layout: A processor has a separate D-cache and an I-cache. D-cache: 64KB, 4-way set associative, block size of 1 word, write-back policy I-cache: 32KB, direct mapped cache, block size of 1 word The processor uses the LRU algorithm for its replacement policy. Answer the following questions. Make sure that you account for all the book-keeping bits. (a) Calculate the number of tag, index and offset bits for the D-cache. (b) Calculate the number of tag, index and offset bits for the I-cache. (c) How many bits are needed to implement the D-cache? (d) How many bits are needed to implement the I-cache?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer Organization and Design The Hardware Software Interface

Authors: David A. Patterson, John L. Hennessy

5th edition

124077269, 978-0124077263

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App