Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Can I have help with computer engineering. Please see attached. VHDL Part I L program to model the circuit whose Using component instantiation of AND

Can I have help with computer engineering. Please see attached. VHDL

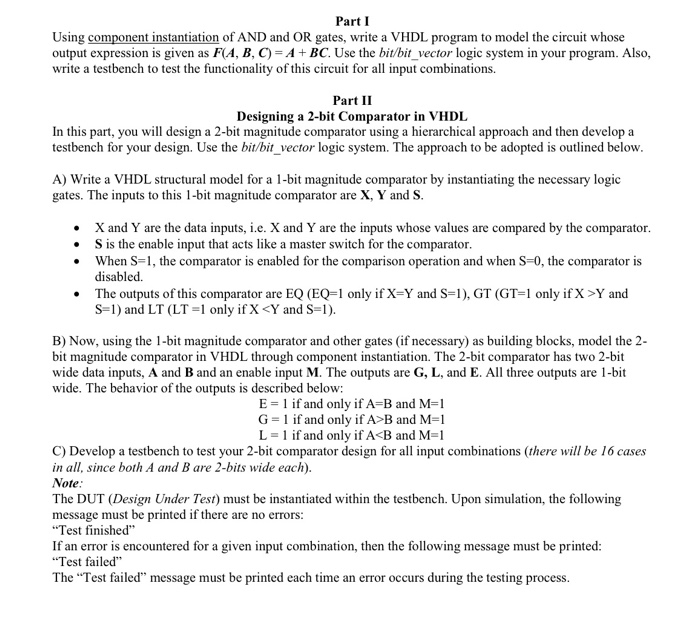

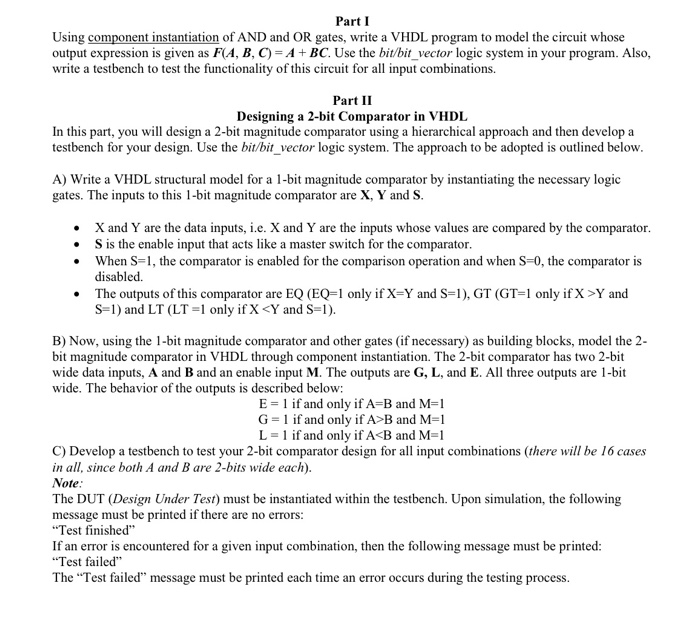

Part I L program to model the circuit whose Using component instantiation of AND and OR gates, write a VHD output expression is given as FA, B, C) A BC. Use the bit/bit vector logic system in your program. Also, write a testbench to test the functionality of this circuit for all input combinations. Part II Designing a 2-bit Comparator in VHDL In this part, you will design a 2-bit magnitude comparator using a hierarchical approach and then develop a testbench for your design. Use the bit/bit vector logic system. The approach to be adopted is outlined below A) Write a VHDL structural model for a 1-bit magnitude comparator by instantiating the necessary logic gates. The inputs to this 1-bit magnitude comparator are X, Y and S X and Y are the data inputs, ie. X and Y are the inputs whose values are compared by the comparator S is the enable input that acts like a master switch for the comparator When S-1, disabled. The outputs of this comparator are EQ (Eq-l only if X-Y and S=l), GT (GT-l only if X-Y and s-1) and LT (LT-1 only if X

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started