CAN SOMEONE EXPLAIN ME THE STEPS IN MORE DETAIL

ARM processor

QUESTION --------------------------

ANSWER --------------------------------------------------------------------

instruction manual------------------

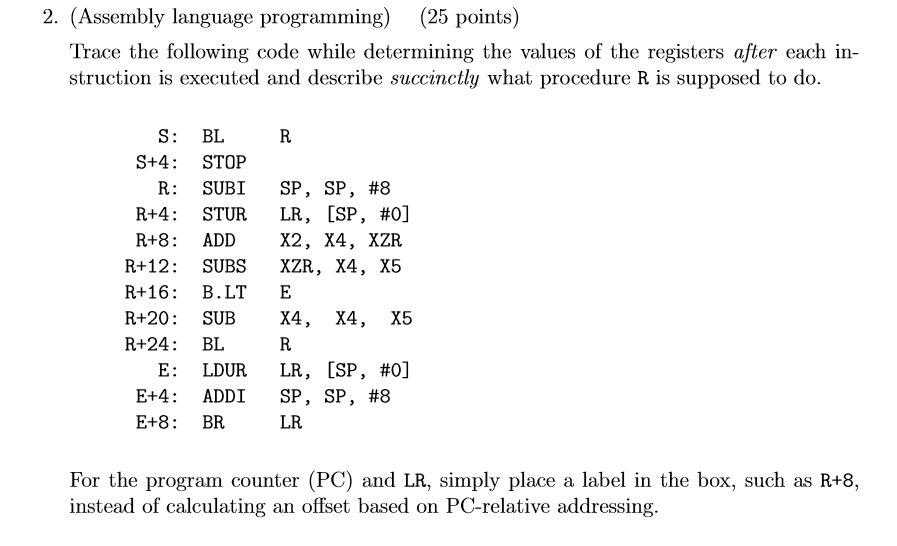

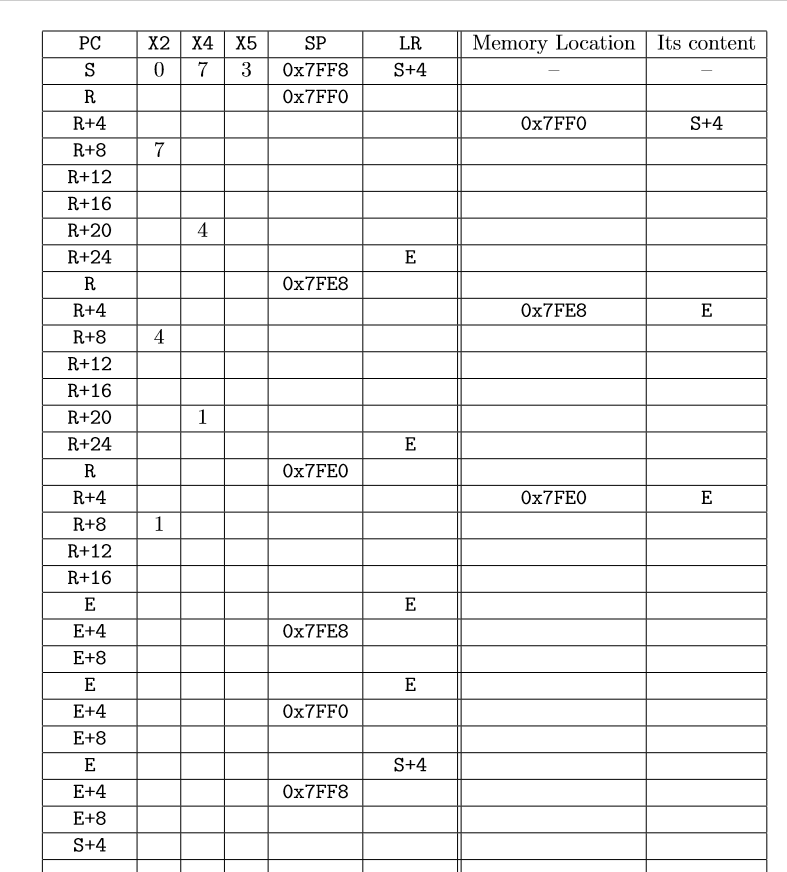

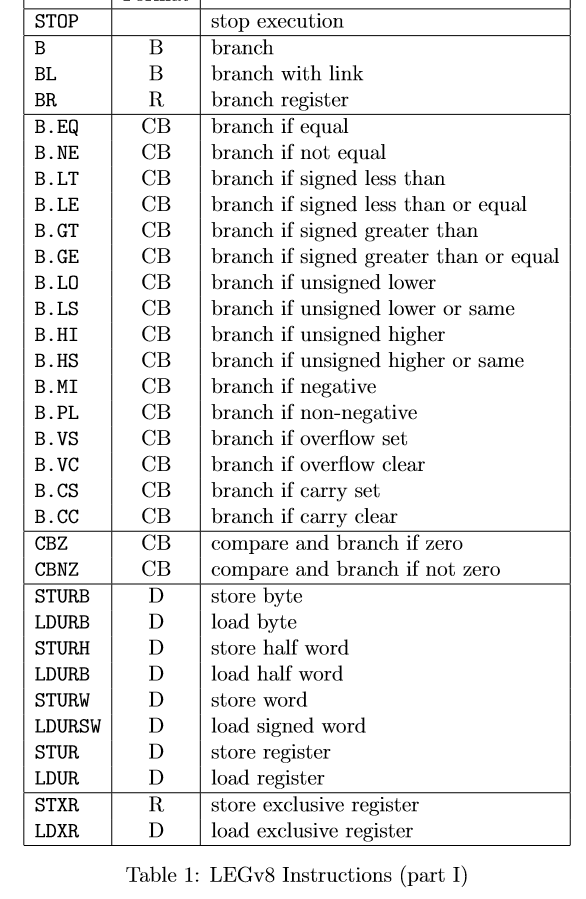

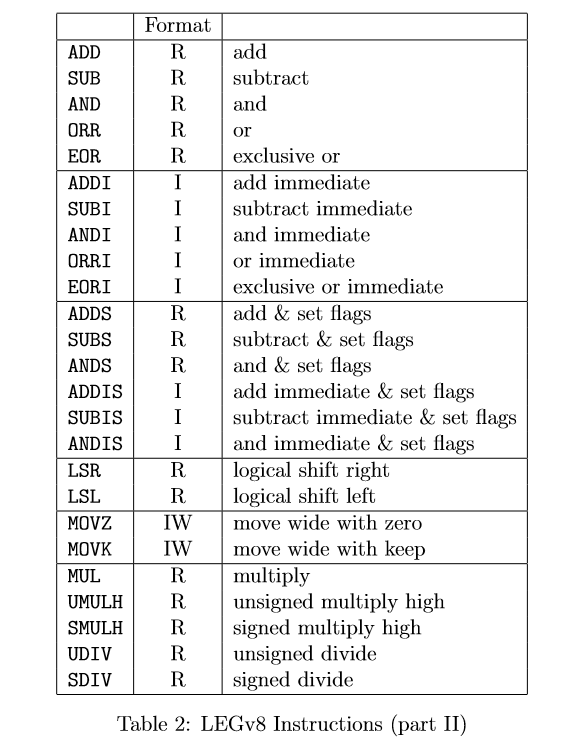

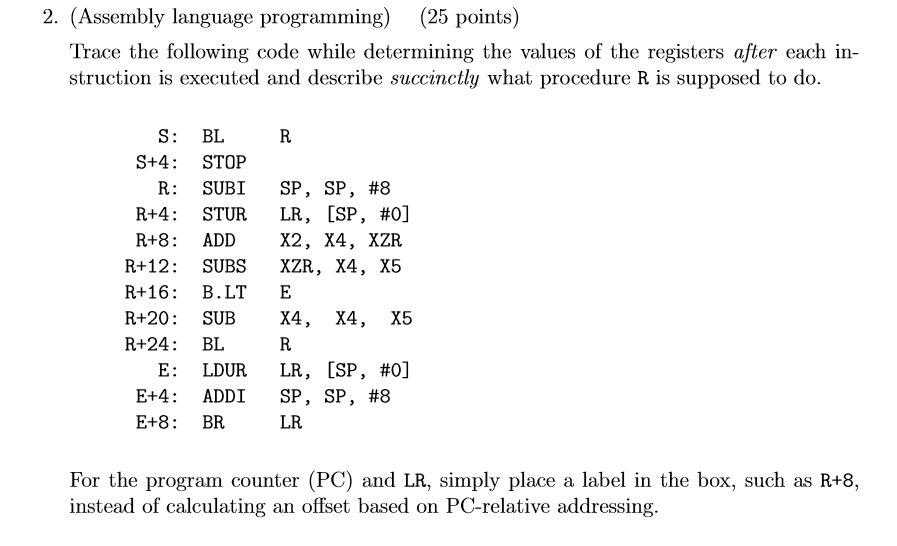

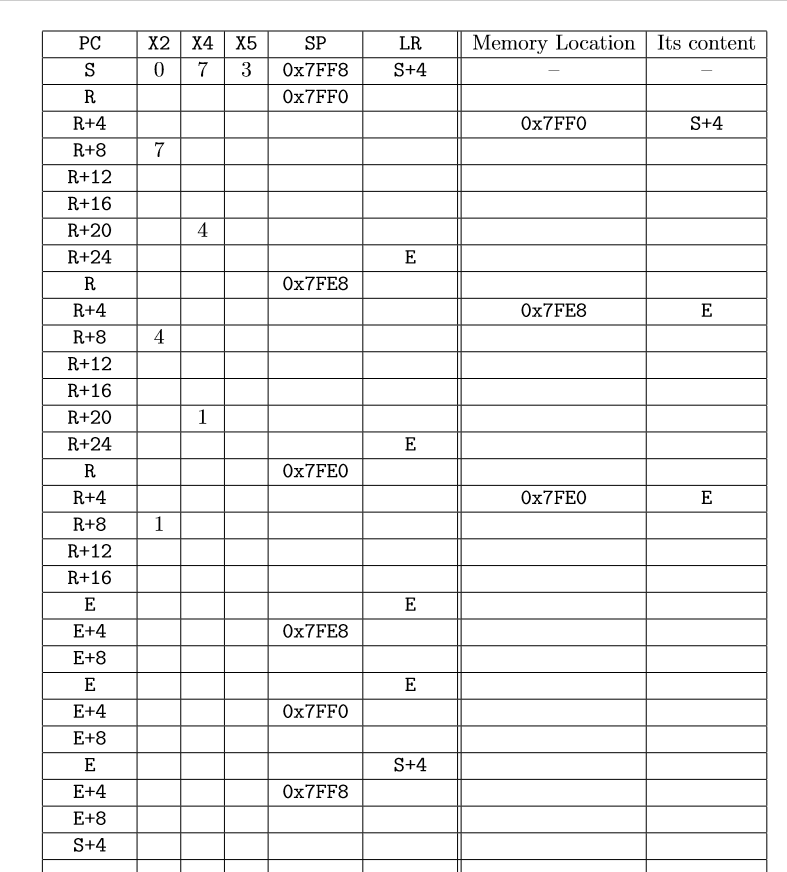

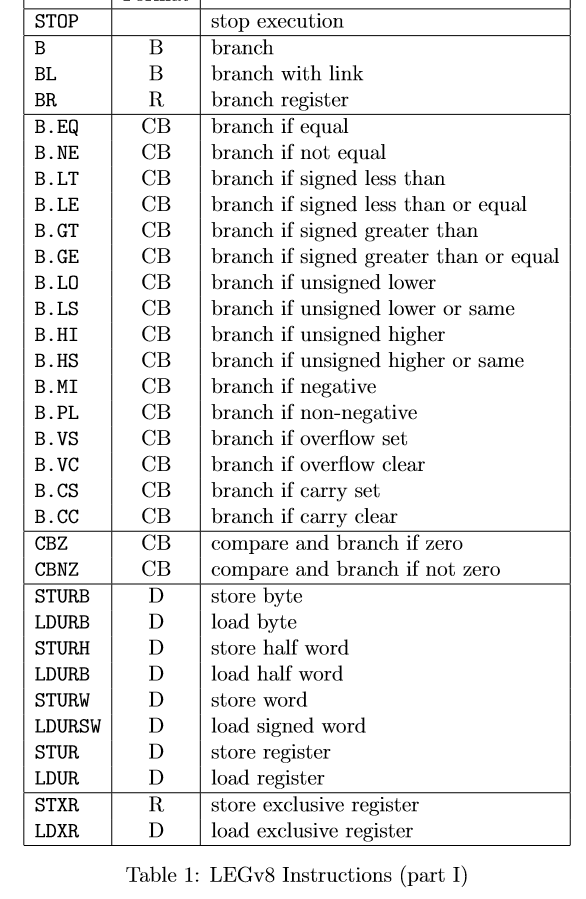

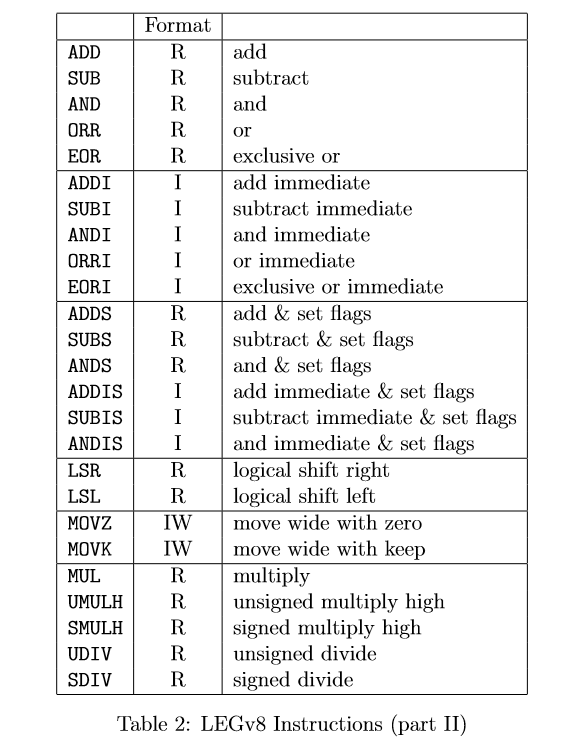

nbly language programming) (25 points) Trace the following code while determining the values of the registers after each in- struction is executed and describe succinctly what procedure R is supposed to do S: BL S+4: STOP R: R+4 : R+8: SUBI STUR ADD SP, LR, X2, X4, XZR SP, #8 [SP, #0] R+12: SUBSXZR, X4, X5 R+16: B.LTE R+20: SUB R+24: BL X4, X4, X5 [SP, SP, #0] #8 E: E+4 : E+8: LDUR ADDI BR LR, SP, LR For the program counter (PC) and LR, simply place a label in the box, such as R+8, instead of calculating an offset based on PC-relative addressing STOP stop execution branch BL BR B.EQ B.NE B.LT B.LE B.GT B.GE B.LO B.LS B.HI .HS B.MI B.PL B.VS B.VC B. CS B.CC CBZ CBNZ STURB LDURB STURH LDURB STURW LDURSWD load signed word STUR LDUR STXR LDXR B branch with link Rbranch register CB branch if equal CBbranch if not equal CBbranch if signed less than CBbranch if signed less than or equal CBbranch if signed greater than CBbranch if signed greater than or equal CBbranch if unsigned lower CBbranch if unsigned lower or same CBbranch if unsigned higher CBbranch if unsigned higher or same CBbranch if negative CBbranch if non-negative CB branch if overflow set CB branch if overflow clear CBbranch if carry set CBbranch if carry clear CBcompare and branch if zero CBcompare and branch if not zero Dstore byte D oad byte D store half word Dload half word store word Dstore register load register Rstore exclusive register Dload exclusive register Table 1: LEGv8 Instructions (part I) Format ADD SUB AND ORR EOR ADDI SUBI ANDI ORRI EORI ADDS SUBS ANDS ADDIS SUBIS ANDIS LSR LSL MOVZ MOVK MUL UMULH SMULHRsigned multiply high UDIV SDIV R add R and Rexclusive or Rsubtract or add immediate subtract immediate and immediate or immediate exclusive or immediate R add & set flags Rsubtract & set flags Rand & set flags Iadd immediate & set flags subtract immediate & set flags and immediate & set flags Rlogical shift right Rlogical shift left IWmove wide with zero IWmove wide with keep R multiply unsigned multiply high unsigned divide signed divide Table 2: LEGv8 Instructions (part II) nbly language programming) (25 points) Trace the following code while determining the values of the registers after each in- struction is executed and describe succinctly what procedure R is supposed to do S: BL S+4: STOP R: R+4 : R+8: SUBI STUR ADD SP, LR, X2, X4, XZR SP, #8 [SP, #0] R+12: SUBSXZR, X4, X5 R+16: B.LTE R+20: SUB R+24: BL X4, X4, X5 [SP, SP, #0] #8 E: E+4 : E+8: LDUR ADDI BR LR, SP, LR For the program counter (PC) and LR, simply place a label in the box, such as R+8, instead of calculating an offset based on PC-relative addressing STOP stop execution branch BL BR B.EQ B.NE B.LT B.LE B.GT B.GE B.LO B.LS B.HI .HS B.MI B.PL B.VS B.VC B. CS B.CC CBZ CBNZ STURB LDURB STURH LDURB STURW LDURSWD load signed word STUR LDUR STXR LDXR B branch with link Rbranch register CB branch if equal CBbranch if not equal CBbranch if signed less than CBbranch if signed less than or equal CBbranch if signed greater than CBbranch if signed greater than or equal CBbranch if unsigned lower CBbranch if unsigned lower or same CBbranch if unsigned higher CBbranch if unsigned higher or same CBbranch if negative CBbranch if non-negative CB branch if overflow set CB branch if overflow clear CBbranch if carry set CBbranch if carry clear CBcompare and branch if zero CBcompare and branch if not zero Dstore byte D oad byte D store half word Dload half word store word Dstore register load register Rstore exclusive register Dload exclusive register Table 1: LEGv8 Instructions (part I) Format ADD SUB AND ORR EOR ADDI SUBI ANDI ORRI EORI ADDS SUBS ANDS ADDIS SUBIS ANDIS LSR LSL MOVZ MOVK MUL UMULH SMULHRsigned multiply high UDIV SDIV R add R and Rexclusive or Rsubtract or add immediate subtract immediate and immediate or immediate exclusive or immediate R add & set flags Rsubtract & set flags Rand & set flags Iadd immediate & set flags subtract immediate & set flags and immediate & set flags Rlogical shift right Rlogical shift left IWmove wide with zero IWmove wide with keep R multiply unsigned multiply high unsigned divide signed divide Table 2: LEGv8 Instructions (part II)