Question

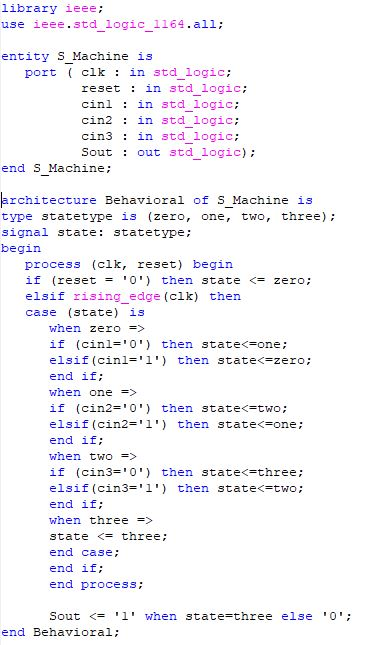

Can someone tell me if this VHDL code and the user contraints file are correct to be implemented on a FPGA board (Numato Spartan 3A).

Can someone tell me if this VHDL code and the user contraints file are correct to be implemented on a FPGA board (Numato Spartan 3A). User constraints is directly from manufacturer. I'm just wondering if my board is somehow defective.

library ieee;

use ieee.std_logic_1164.all;

entity S_Machine is

port ( clk : in std_logic;

reset : in std_logic;

cin1 : in std_logic;

cin2 : in std_logic;

cin3 : in std_logic;

Sout : out std_logic);

end S_Machine;

architecture Behavioral of S_Machine is

type statetype is (zero, one, two, three);

signal state: statetype;

begin

process (clk, reset) begin

if (reset = '0') then state

elsif rising_edge(clk) then

case (state) is

when zero =>

if (cin1='0') then state

elsif(cin1='1') then state

end if;

when one =>

if (cin2='0') then state

elsif(cin2='1') then state

end if;

when two =>

if (cin3='0') then state

elsif(cin3='1') then state

end if;

when three =>

state

end case;

end if;

end process;

Sout

end Behavioral;

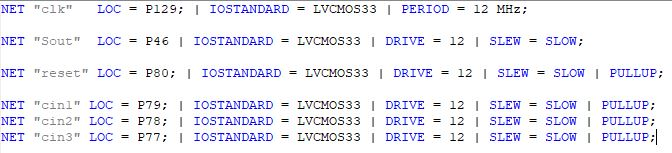

NET "clk" LOC = P129; | IOSTANDARD = LVCMOS33 | PERIOD = 12 MHz;

NET "Sout" LOC = P46 | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = SLOW;

NET "reset" LOC = P80; | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = SLOW | PULLUP;

NET "cin1" LOC = P79; | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = SLOW | PULLUP;

NET "cin2" LOC = P78; | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = SLOW | PULLUP;

NET "cin3" LOC = P77; | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = SLOW | PULLUP;

library ieee use ieee.std logic 1164.all: entity S Machine is port clk: in std_logic: reset in std_logic: cinl: in std logic: cin2: in std logic: cin3 : in std logic Sout out std logic); end S Machine; architecture Behavioral of S Machine is type statetype is (zero, one, two, three) signal state statetype; begin process (clk, reset) begin if (reset= '0') then state if (cin!= "O ') then state state if (cin!= "O ') then state stateStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started