CAN YOU HELP ME , PLEASE HELP URGENTLY !! I NEED YOU SO MUCH AND I WILL BE GRATEFUL ! PLEASE CAN AN EXPERT AT VERILOG ANSWER MY QUESTION AS SOON AS POSSIBLE ! HELP

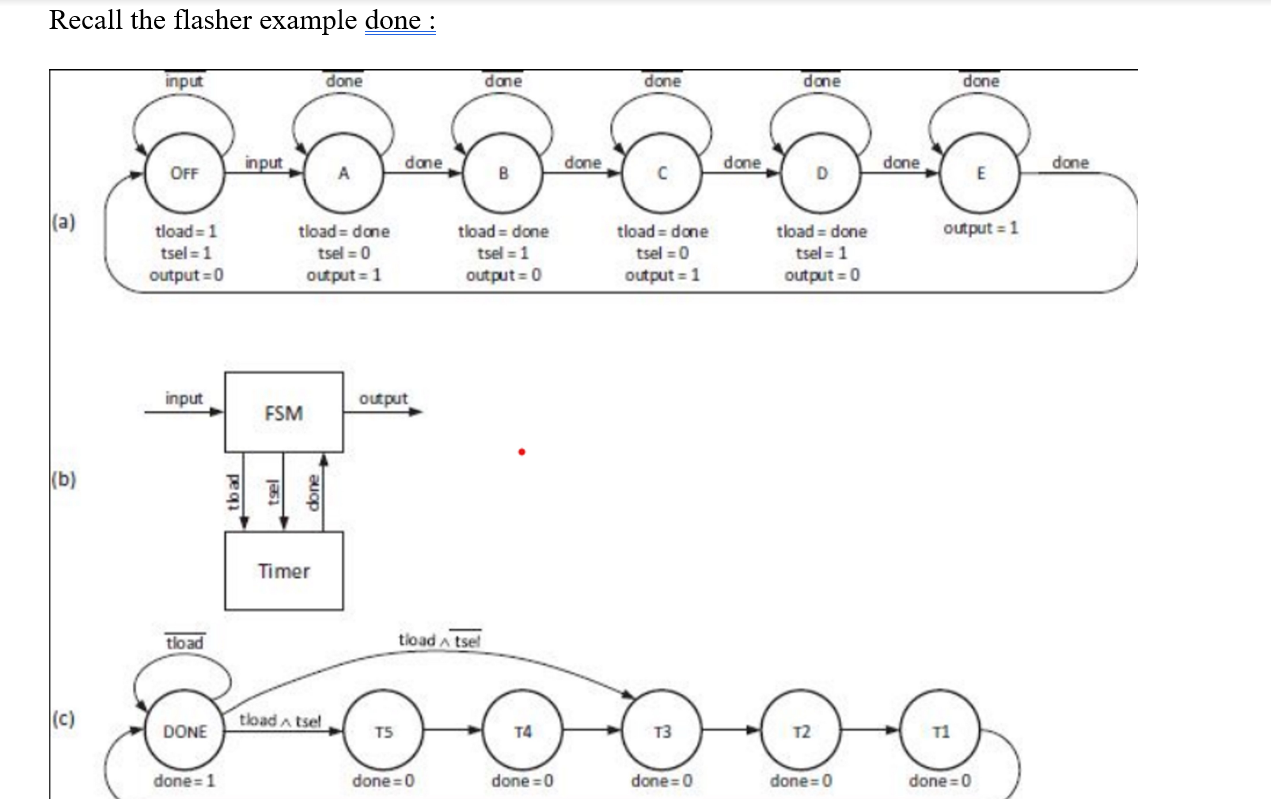

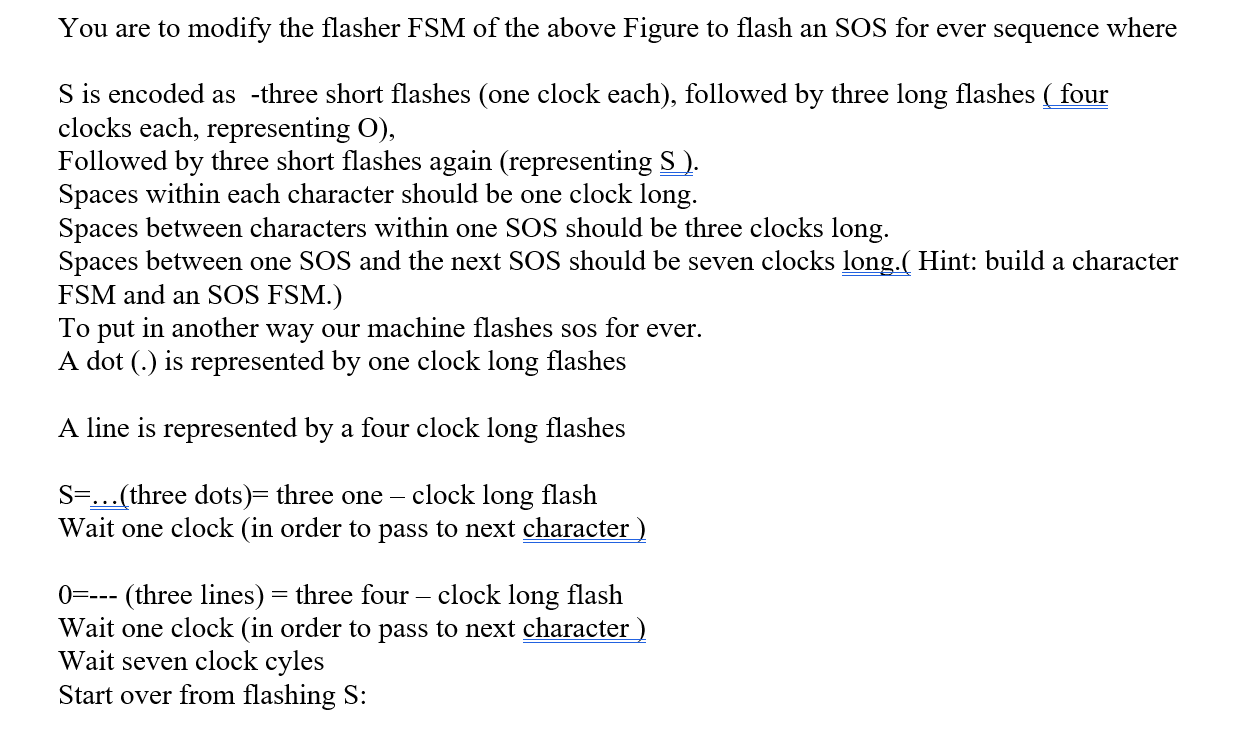

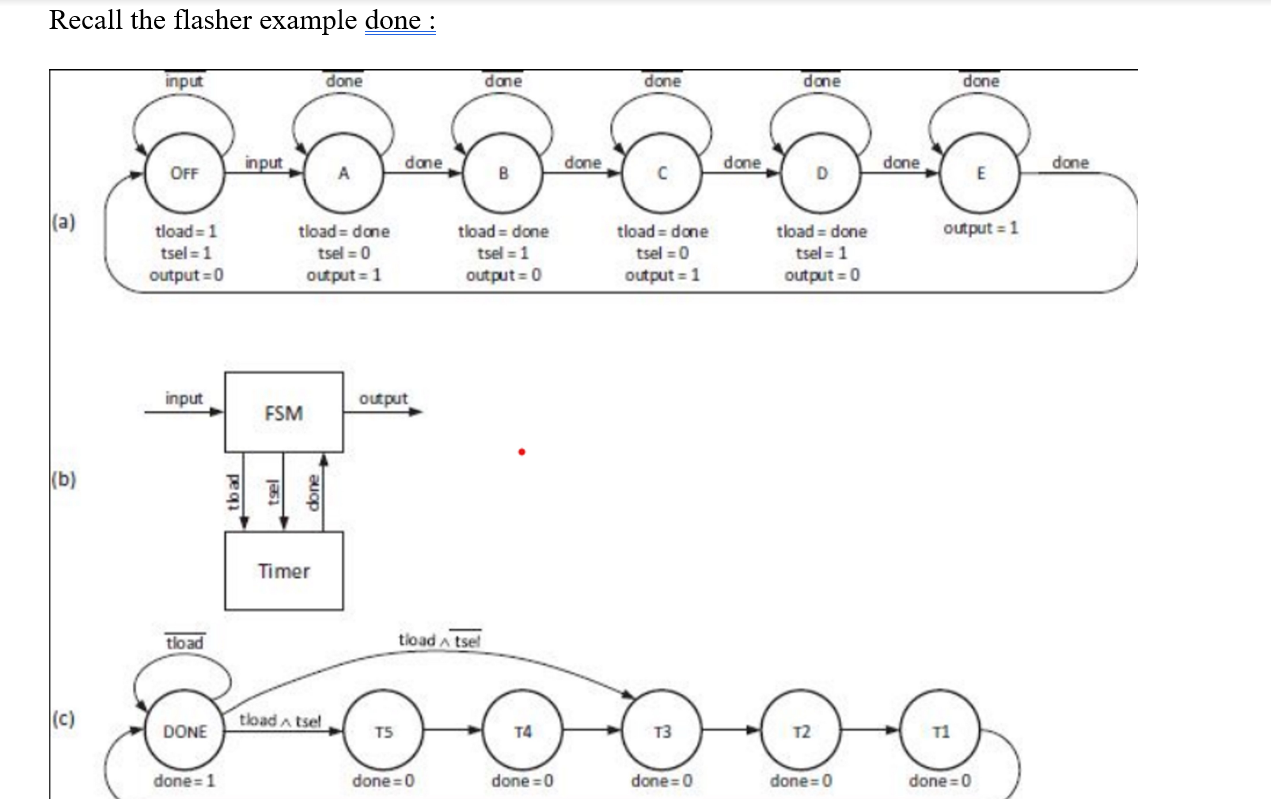

Recall the flasher example done : input done done done done done input done OFF done done done done A B D E (a) output = 1 tload=1 tsel = 1 output=0 tload= done tsel = 0 output = 1 tload = done tsel = 1 output = 0 tload = done tsel=0 output = 1 tload = done tsel = 1 output = 0 input output FSM (b) tbad Eugp Timer tload tload Atsel (c) tload Atsel DONE T5 T4 T3 T2 T1 done=1 done=0 done=0 done=0 done=0 done=0 You are to modify the flasher FSM of the above Figure to flash an SOS for ever sequence where S is encoded as -three short flashes (one clock each), followed by three long flashes ( four clocks each, representing O), Followed by three short flashes again (representing S). Spaces within each character should be one clock long. Spaces between characters within one SOS should be three clocks long. Spaces between one SOS and the next SOS should be seven clocks long. ( Hint: build a character FSM and an SOS FSM.) To put in another way our machine flashes sos for ever. A dot (.) is represented by one clock long flashes A line is represented by a four clock long flashes S=... (three dots)= three one - clock long flash Wait one clock (in order to pass to next character ) 0=--- (three lines) = three four clock long flash Wait one clock in order to pass to next character ) Wait seven clock cyles Start over from flashing S: Deliverables : A) Block diagram of the Fsm ( something like section b of the figre but slightly more complex) B) State diagram of the each FSM you have specified in part a. C) Verilog implementation of the system. Each modle should be in its own ascii file. D) Verilog Project (in zipped format) E) Test bench Recall the flasher example done : input done done done done done input done OFF done done done done A B D E (a) output = 1 tload=1 tsel = 1 output=0 tload= done tsel = 0 output = 1 tload = done tsel = 1 output = 0 tload = done tsel=0 output = 1 tload = done tsel = 1 output = 0 input output FSM (b) tbad Eugp Timer tload tload Atsel (c) tload Atsel DONE T5 T4 T3 T2 T1 done=1 done=0 done=0 done=0 done=0 done=0 You are to modify the flasher FSM of the above Figure to flash an SOS for ever sequence where S is encoded as -three short flashes (one clock each), followed by three long flashes ( four clocks each, representing O), Followed by three short flashes again (representing S). Spaces within each character should be one clock long. Spaces between characters within one SOS should be three clocks long. Spaces between one SOS and the next SOS should be seven clocks long. ( Hint: build a character FSM and an SOS FSM.) To put in another way our machine flashes sos for ever. A dot (.) is represented by one clock long flashes A line is represented by a four clock long flashes S=... (three dots)= three one - clock long flash Wait one clock (in order to pass to next character ) 0=--- (three lines) = three four clock long flash Wait one clock in order to pass to next character ) Wait seven clock cyles Start over from flashing S: Deliverables : A) Block diagram of the Fsm ( something like section b of the figre but slightly more complex) B) State diagram of the each FSM you have specified in part a. C) Verilog implementation of the system. Each modle should be in its own ascii file. D) Verilog Project (in zipped format) E) Test bench