Answered step by step

Verified Expert Solution

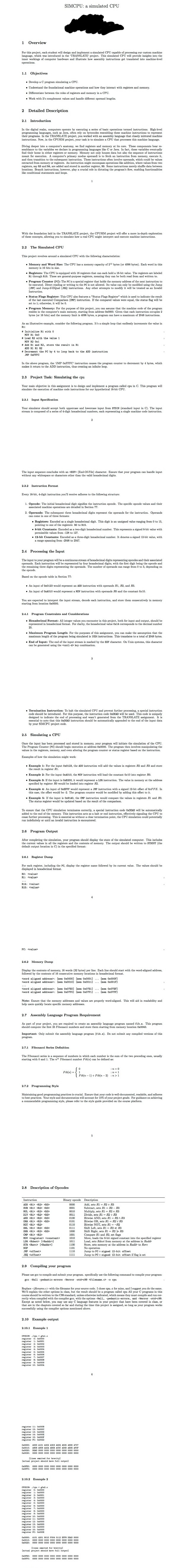

Question

1 Approved Answer

can you help me with the code where my pc count in not working properly. when in pass this text as in input A

can you help me with the code where my pc count in not working properly. when in pass this text as in input AAAAAAAAAAAAAABBACCADDAEEAFF the output for pc should be but it was and here is my code:

#include

#include

#define MEMORYSIZE

#define REGISTERCOUNT

typedef struct

unsigned short memoryMEMORYSIZE;

unsigned short registersREGISTERCOUNT;

unsigned short pc;

unsigned short statusflags;

CPU;

void initializecpuCPU cpu

memsetcpumemory, sizeofcpumemory;

memsetcpuregisters, sizeofcpuregisters;

cpupc ;

cpustatusflags ;

void processinputCPU cpu

unsigned short instruction;

int i ;

while scanfhx &instruction EOF

cpumemoryi instruction;

printf from process:X

instruction;

cpumemoryixDEAD; Termination instruction

void simulatecpuCPU cpu

while cpumemorycpupcxDEAD

unsigned short instruction cpumemorycpupc;

unsigned short opcode instruction ;

unsigned short operands instruction & xFFF;

switch opcode

case x: ADD

case x: SUB

case x: MUL

case x: DIV

case x: AND

case x: ORR

unsigned short roperands & xF;

unsigned short roperands & xF;

unsigned short r operands & xF;

cpuregistersropcode xcpuregistersr cpuregistersr :

opcode xcpuregistersr cpuregistersr :

opcode xcpuregistersr cpuregistersr :

opcode xcpuregistersr cpuregistersr :

opcode xcpuregistersr & cpuregistersr :

cpuregistersr cpuregistersr;

break;

case x: NOT

unsigned short roperands & xF;

unsigned short roperands & xF;

cpuregistersr ~cpuregistersr;

break;

case xA: MOV

unsigned short r operands & xF;

unsigned short constant operands & xFF;

cpuregistersr constant;

break;

case xB: LDR

unsigned short rdest operands & xF;

unsigned short raddr operands & xF;

cpuregistersrdest cpumemorycpuregistersraddr;

break;

case xC: STR

unsigned short rsrc operands & xF;

unsigned short raddr operands & xF;

cpumemorycpuregistersraddr cpuregistersrsrc;

break;

case xE: JMP

short offset operands & xFFF;

if offset & x

offset xF;

cpupc offset;

break;

case xF: JEQ

if cpustatusflags

short offset operands & xFFF;

if offset & x

offset xF;

cpupc offset;

break;

default:

printfInvalid opcode: X

opcode;

return;

void displayoutputCPU cpu

for int i ; i REGISTERCOUNT; i

printfregister d: xX

i cpuregistersi;

printfregister PC: xX

cpupc;

for int i ; i MEMORYSIZE; i

printfxX: i;

for int j ; j ; j

if i j MEMORYSIZE

printfX cpumemoryi j;

printf

;

int main

CPU cpu;

initializecpu&cpu;

processinput&cpu;

simulatecpu&cpu;

displayoutput&cpu;

return ;

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started