Question

c)If the sequence of instructions will be run on a 5-stage Pipelined MIPS processor that has hazard detection, NO forwarding, RegFile output comparator, and a

c)If the sequence of instructions will be run on a 5-stage Pipelined MIPS processor that has hazard detection, NO forwarding, RegFile output comparator, and a hardware controlled stall of one clock cycle for branch instructions between id and ex stage, determine the total number of clock cycles needed to execute the instructions

Rewrite the original sequence of instructions given and insert nop instructions where stalls must be used according to your analysis in part c).

e) If the sequence of instructions will be run on a 5-stage Pipelined MIPS processor that has hazard detection, forwarding, determine the number of clock cycles needed to execute the instructions. Use stalls only when necessary. Use a pipeline timing diagram to show your work and draw an arrow between stages of execution where data is forwarded

f) Rewrite the original sequence of instructions given and insert nop instruy. Use a pipeline timing diagram to show your work and draw an arrow between stages of execution where data is forwardedzctions where stalls must be used according to youranalysis

Some help on any of these would be great! Thanks!

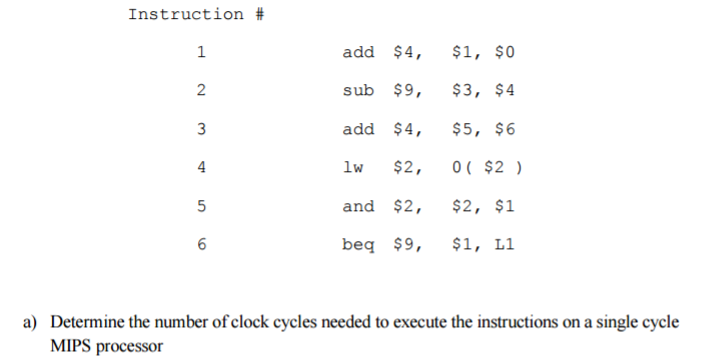

Instruction add $4, $1, $0 sub $9, S3, $4 add $4, $5, $6 lw $2, 0 2 and $2, $2, $1 be $9, $1 L1. a) Determine the number of clock cycles needed to execute the instructions on a single cycle MIPS processorStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started