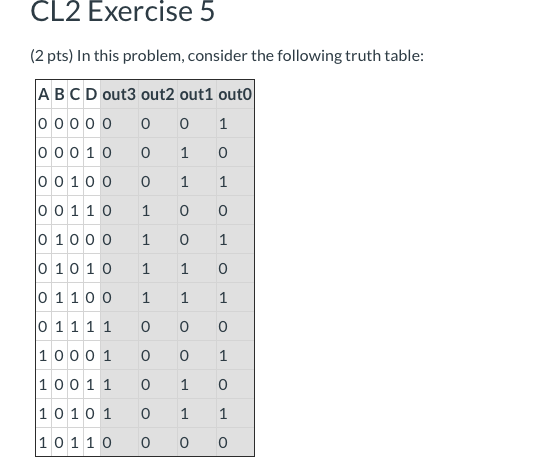

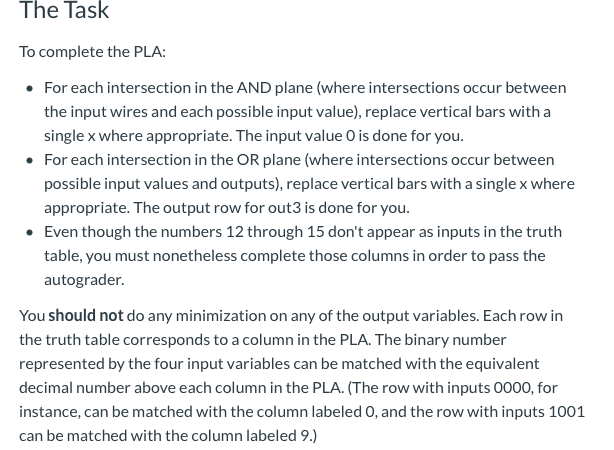

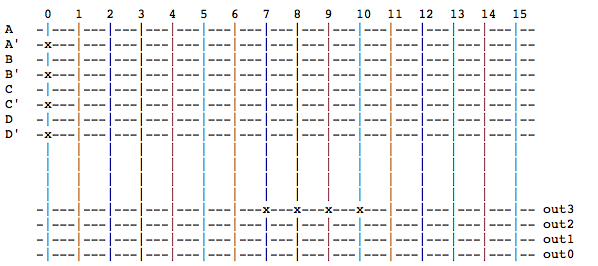

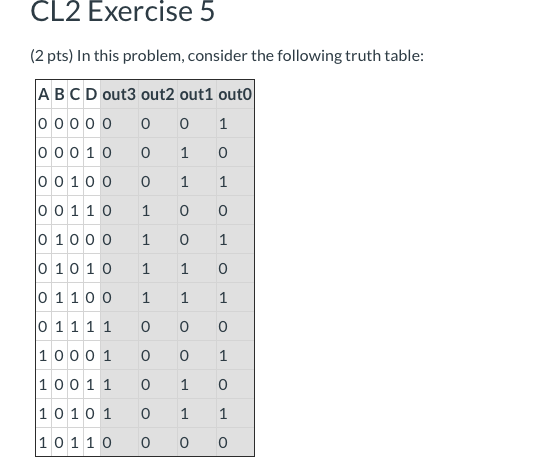

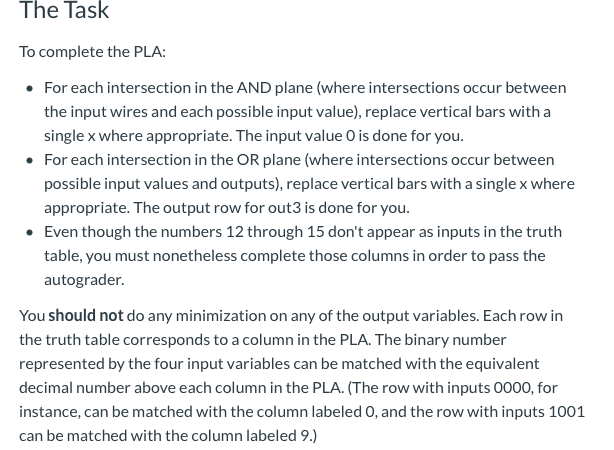

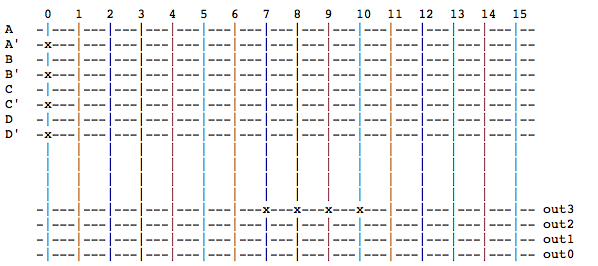

CL2 Exercise 5 (2 pts) In this problem, consider the following truth table: ABC D out3 out2 out1 outo 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 1 0 1 1 0 0 0 0 The Task To complete the PLA: For each intersection in the AND plane (where intersections occur between the input wires and each possible input value), replace vertical bars with a single x where appropriate. The input value 0 is done for you. For each intersection in the OR plane (where intersections occur between possible input values and outputs), replace vertical bars with a single x where appropriate. The output row for out3 is done for you. Even though the numbers 12 through 15 don't appear as inputs in the truth table, you must nonetheless complete those columns in order to pass the autograder. You should not do any minimization on any of the output variables. Each row in the truth table corresponds to a column in the PLA. The binary number represented by the four input variables can be matched with the equivalent decimal number above each column in the PLA. (The row with inputs 0000, for instance, can be matched with the column labeled 0, and the row with inputs 1001 can be matched with the column labeled 9.) ----- out3 ---|-- out2 -- out1 ----- out0 --- ! ! ! ! ! ! | ! ! ! ! | ! | 10 11 12 13 14 15 9 8 X 7 ===X=== 6 H H H H ! ! ! ! ! ! ! ! 5 ! ! ! ! ! 4 3 ! 2 1 CL2 Exercise 5 (2 pts) In this problem, consider the following truth table: ABC D out3 out2 out1 outo 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 1 0 1 1 0 0 0 0 The Task To complete the PLA: For each intersection in the AND plane (where intersections occur between the input wires and each possible input value), replace vertical bars with a single x where appropriate. The input value 0 is done for you. For each intersection in the OR plane (where intersections occur between possible input values and outputs), replace vertical bars with a single x where appropriate. The output row for out3 is done for you. Even though the numbers 12 through 15 don't appear as inputs in the truth table, you must nonetheless complete those columns in order to pass the autograder. You should not do any minimization on any of the output variables. Each row in the truth table corresponds to a column in the PLA. The binary number represented by the four input variables can be matched with the equivalent decimal number above each column in the PLA. (The row with inputs 0000, for instance, can be matched with the column labeled 0, and the row with inputs 1001 can be matched with the column labeled 9.) ----- out3 ---|-- out2 -- out1 ----- out0 --- ! ! ! ! ! ! | ! ! ! ! | ! | 10 11 12 13 14 15 9 8 X 7 ===X=== 6 H H H H ! ! ! ! ! ! ! ! 5 ! ! ! ! ! 4 3 ! 2 1