Question

Code for Project 2b module project2b(a,b,d,S,V, Cin, Cout); input [31:0] a,b; output [31:0] d; input [2:0] S; output Cout, V; input Cin; wire [31:0] gint,

Code for Project 2b

module project2b(a,b,d,S,V, Cin, Cout); input [31:0] a,b; output [31:0] d; input [2:0] S; output Cout, V; input Cin; wire [31:0] gint, pint, cint; wire [31:0] Coutint; wire gout, pout; lac32 x0(.g(gint), .p(pint), .c(cint), .gout(gout), .pout(pout), .cin(Cin)); alu32 x1(.a(a), .b(b), .sum(d), .sel(S), .g(gint), .p(pint), .Cin(cint)); //assign cint[0]=Cin; assign Cout=gout | pout & Cin; assign V= Cout ^ cint[31]; endmodule

//////////////////////////////////

//alu 1 bit module alu1(a,b,sum, sel, g, p, Cin); input a,b, Cin; input [2:0] sel; output sum, g, p; reg sum; wire bint, cint; assign bint = b ^ sel[0]; assign cint = Cin & sel[1]; assign g = a & bint; assign p = a ^ bint; always @(*) begin case (sel) 3'b000: sum = a ^ b; 3'b001: sum =~(a ^ b); 3'b010: sum = p ^ cint; 3'b011: sum = p ^ cint; 3'b100: sum = a | b; 3'b101: sum = ~(a | b); 3'b110: sum = a & b; default: sum =1'b0; endcase end endmodule

////////////////////////////////////// //ALU 32 BIT ////////////////////////////////////// module alu32 (a,b,sum, sel, g, p, Cin); input [31:0] a,b, Cin; output [31:0] sum, g,p; input [2:0] sel; //module alu1(a,b,sum, sel, g, p, Cin); alu1 ax0(a[0], b[0], sum[0], sel, g[0], p[0], Cin[0]); alu1 ax1(a[1], b[1], sum[1], sel, g[1], p[1], Cin[1]); alu1 ax2(a[2], b[2], sum[2], sel, g[2], p[2], Cin[2]); alu1 ax3(a[3], b[3], sum[3], sel, g[3], p[3], Cin[3]); alu1 ax4(a[4], b[4], sum[4], sel, g[4], p[4], Cin[4]); alu1 ax5(a[5], b[5], sum[5], sel, g[5], p[5], Cin[5]); alu1 ax6(a[6], b[6], sum[6], sel, g[6], p[6], Cin[6]); alu1 ax7(a[7], b[7], sum[7], sel, g[7], p[7], Cin[7]); alu1 ax8(a[8], b[8], sum[8], sel, g[8], p[8], Cin[8]); alu1 ax9(a[9], b[9], sum[9], sel, g[9], p[9], Cin[9]); alu1 ax10(a[10], b[10], sum[10], sel, g[10], p[10], Cin[10]); alu1 ax11(a[11], b[11], sum[11], sel, g[11], p[11], Cin[11]); alu1 ax12(a[12], b[12], sum[12], sel, g[12], p[12], Cin[12]); alu1 ax13(a[13], b[13], sum[13], sel, g[13], p[13], Cin[13]); alu1 ax14(a[14], b[14], sum[14], sel, g[14], p[14], Cin[14]); alu1 ax15(a[15], b[15], sum[15], sel, g[15], p[15], Cin[15]); alu1 ax16(a[16], b[16], sum[16], sel, g[16], p[16], Cin[16]); alu1 ax17(a[17], b[17], sum[17], sel, g[17], p[17], Cin[17]); alu1 ax18(a[18], b[18], sum[18], sel, g[18], p[18], Cin[18]); alu1 ax19(a[19], b[19], sum[19], sel, g[19], p[19], Cin[19]); alu1 ax20(a[20], b[20], sum[20], sel, g[20], p[20], Cin[20]); alu1 ax21(a[21], b[21], sum[21], sel, g[21], p[21], Cin[21]); alu1 ax22(a[22], b[22], sum[22], sel, g[22], p[22], Cin[22]); alu1 ax23(a[23], b[23], sum[23], sel, g[23], p[23], Cin[23]); alu1 ax24(a[24], b[24], sum[24], sel, g[24], p[24], Cin[24]); alu1 ax25(a[25], b[25], sum[25], sel, g[25], p[25], Cin[25]); alu1 ax26(a[26], b[26], sum[26], sel, g[26], p[26], Cin[26]); alu1 ax27(a[27], b[27], sum[27], sel, g[27], p[27], Cin[27]); alu1 ax28(a[28], b[28], sum[28], sel, g[28], p[28], Cin[28]); alu1 ax29(a[29], b[29], sum[29], sel, g[29], p[29], Cin[29]); alu1 ax30(a[30], b[30], sum[30], sel, g[30], p[30], Cin[30]); alu1 ax31(a[31], b[31], sum[31], sel, g[31], p[31], Cin[31]); endmodule

/////////////// //LAC Design//// ////////////// module lac2(g,p,c, gout, pout, cin); input [1:0] g,p; output [1:0] c; output gout, pout; input cin; assign gout= g[1]| (g[0] & p[1]); assign pout= p[1]& p[0]; assign c[1]=g[0]| (p[0] & cin); assign c[0]=cin; endmodule

module lac4(g,p,c, gout, pout, cin); input [3:0] g,p; output [3:0] c; output gout, pout; input cin; wire [1:0] gint, pint, cint; lac2 a0(.g(g[3:2]), .p(p[3:2]), .c(c[3:2]), .gout(gint[1]), .pout(pint[1]), .cin(cint[1])); lac2 a1(.g(g[1:0]), .p(p[1:0]), .c(c[1:0]), .gout(gint[0]), .pout(pint[0]), .cin(cint[0])); lac2 a2(.g(gint), .p(pint), .c(cint), .gout(gout), .pout(pout), .cin(cin)); endmodule

module lac8(g,p,c, gout, pout, cin); input [7:0] g,p; output [7:0] c; output gout, pout; input cin; wire [1:0] gint, pint, cint; lac4 a0(.g(g[7:4]), .p(p[7:4]), .c(c[7:4]), .gout(gint[1]), .pout(pint[1]), .cin(cint[1])); lac4 a1(.g(g[3:0]), .p(p[3:0]), .c(c[3:0]), .gout(gint[0]), .pout(pint[0]), .cin(cint[0])); lac2 a2(.g(gint), .p(pint), .c(cint), .gout(gout), .pout(pout), .cin(cin)); endmodule

module lac16(g,p,c, gout, pout, cin); input [15:0] g,p; output [15:0] c; output gout, pout; input cin; wire [1:0] gint, pint, cint; lac8 a0(.g(g[15:8]), .p(p[15:8]), .c(c[15:8]), .gout(gint[1]), .pout(pint[1]), .cin(cint[1])); lac8 a1(.g(g[7:0]), .p(p[7:0]), .c(c[7:0]), .gout(gint[0]), .pout(pint[0]), .cin(cint[0])); lac2 a2(.g(gint), .p(pint), .c(cint), .gout(gout), .pout(pout), .cin(cin)); endmodule

module lac32(g,p,c, gout, pout, cin); input [31:0] g,p; output [31:0] c; output gout, pout; input cin; wire [1:0] gint, pint, cint; lac16 a0(.g(g[31:16]), .p(p[31:16]), .c(c[31:16]), .gout(gint[1]), .pout(pint[1]), .cin(cint[1])); lac16 a1(.g(g[15:0]), .p(p[15:0]), .c(c[15:0]), .gout(gint[0]), .pout(pint[0]), .cin(cint[0])); lac2 a2(.g(gint), .p(pint), .c(cint), .gout(gout), .pout(pout), .cin(cin)); endmodule

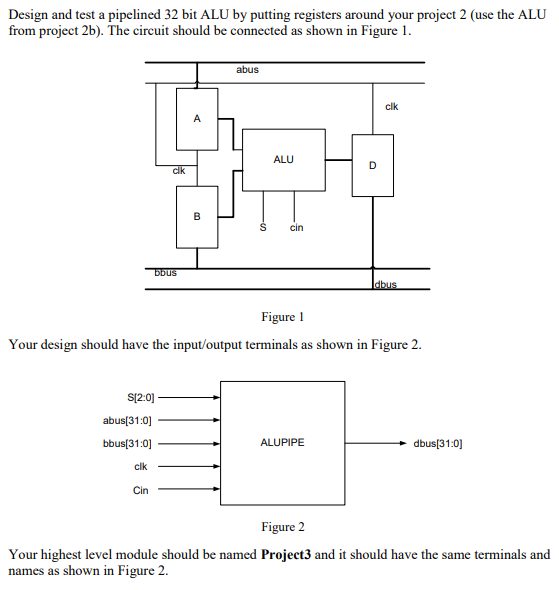

Design and test a pipelined 32 bit ALU by putting registers around your project 2 (use the ALU from project 2b). The circuit should be connected as shown in Figure 1. abus clk A ALU D clk B S cin bbus dbus Figure 1 Your design should have the input/output terminals as shown in Figure 2. S[2:0) abus[31:0) bbus[31:0) ALUPIPE dbus[31:0) clk Cin Figure 2 Your highest level module should be named Project3 and it should have the same terminals and names as shown in Figure 2. Design and test a pipelined 32 bit ALU by putting registers around your project 2 (use the ALU from project 2b). The circuit should be connected as shown in Figure 1. abus clk A ALU D clk B S cin bbus dbus Figure 1 Your design should have the input/output terminals as shown in Figure 2. S[2:0) abus[31:0) bbus[31:0) ALUPIPE dbus[31:0) clk Cin Figure 2 Your highest level module should be named Project3 and it should have the same terminals and names as shown in Figure 2Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started