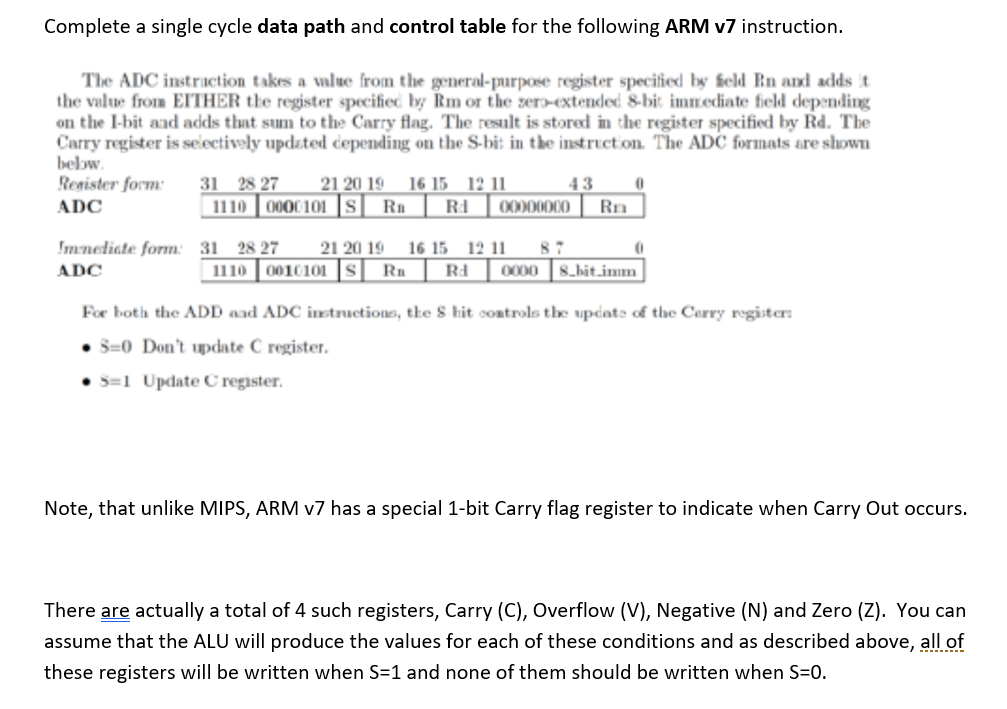

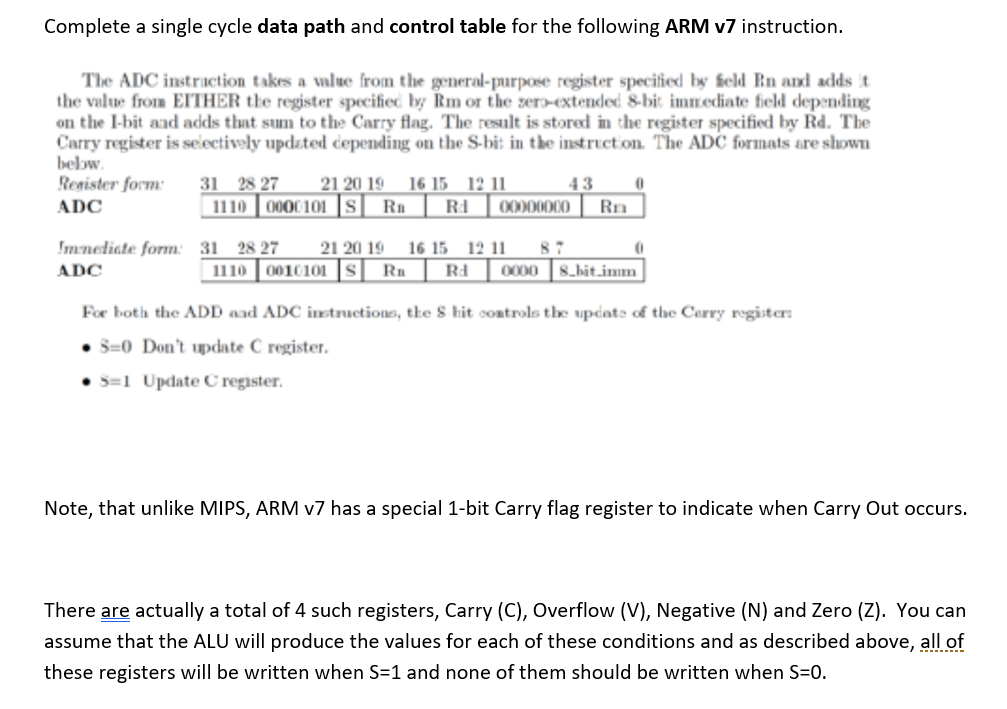

Complete a single cycle data path and control table for the following ARM v7 instruction. The ADC instraction takes a alue from the general-pmurpose register speciied by feld En and adds t the value from ETTHER the register specified by Rm or the zer-extended 8 -bit imediate feld depending on the I-bit aad adds that sum to the Carry flag. The resilt is stored in the register specified by Rd. The Carry register is selectively updated cepending on the S-bi: in the instruction. The ADC formats are shown below Resister form 31 2827 212019 1615 1211 ADC 43 0 mnediate form: 31 2827 2120 19 16 15 1187 ADC 110 0010101 S R 11 10 011 101 Rn Rd 0000 S hit.im For both the ADD aad ADC intuctions,the S hit costrols the upiate of the Cerry register 3-0 Don't update C register S-1 Update C register Note, that unlike MIPS, ARM v7 has a special 1-bit Carry flag register to indicate when Carry Out occurs. There are actually a total of 4 such registers, Carry (C), Overflow (V), Negative (N) and Zero (Z). You can assume that the ALU will produce the values for each of these conditions and as described above, all of these registers will be written when S-1 and none of them should be written when S-0. Complete a single cycle data path and control table for the following ARM v7 instruction. The ADC instraction takes a alue from the general-pmurpose register speciied by feld En and adds t the value from ETTHER the register specified by Rm or the zer-extended 8 -bit imediate feld depending on the I-bit aad adds that sum to the Carry flag. The resilt is stored in the register specified by Rd. The Carry register is selectively updated cepending on the S-bi: in the instruction. The ADC formats are shown below Resister form 31 2827 212019 1615 1211 ADC 43 0 mnediate form: 31 2827 2120 19 16 15 1187 ADC 110 0010101 S R 11 10 011 101 Rn Rd 0000 S hit.im For both the ADD aad ADC intuctions,the S hit costrols the upiate of the Cerry register 3-0 Don't update C register S-1 Update C register Note, that unlike MIPS, ARM v7 has a special 1-bit Carry flag register to indicate when Carry Out occurs. There are actually a total of 4 such registers, Carry (C), Overflow (V), Negative (N) and Zero (Z). You can assume that the ALU will produce the values for each of these conditions and as described above, all of these registers will be written when S-1 and none of them should be written when S-0