Question: Computer Architecture The basic single-cycle MIPS implementation in Figure 4.2 (pp. 247) can only implement some instructions. New instructions can be added to an existing

Computer Architecture

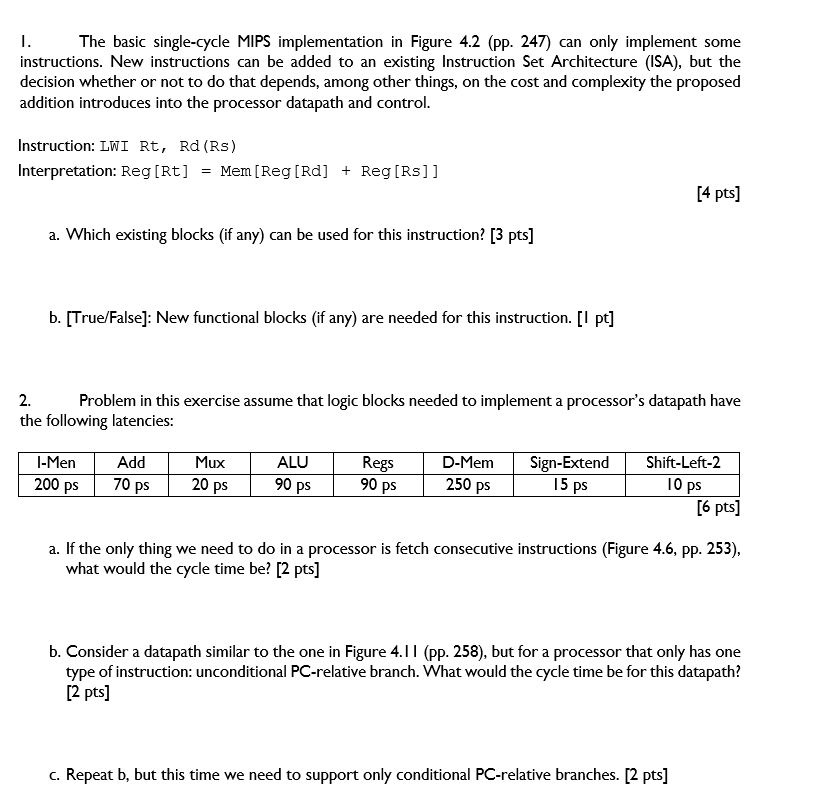

The basic single-cycle MIPS implementation in Figure 4.2 (pp. 247) can only implement some instructions. New instructions can be added to an existing Instruction Set Architecture (ISA), but the decision whether or not to do that depends, among other things, on the cost and complexity the proposed addition introduces into the processor datapath and control Instruction: LWI Rt, Rd (Rs) Interpretation: Reg [Rt] = Mem [Reg[Rd] + Reg [RS]] [4 pts] a. Which existing blocks (if any) can be used for this instruction? [3 pts] b. [True/False]: New functional blocks (if any) are needed for this instruction. [l pt] 2. the following latencies: Problem in this exercise assume that logic blocks needed to implement a processor's datapath have -Men 200 ps70 ps D-Mem Sign-Extend 250 ps Add uX ALU Re Shift-Left-2 gs ps 20 ps ps ps ps [6 pts] a. If the only thing we need to do in a processor is fetch consecutive instructions (Figure 4.6, pp. 253), what would the cycle time be? [2 pts] b. Consider a datapath similar to the one in Figure 4.1 1 (pp. 258), but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath? [2 pts] c. Repeat b, but this time we need to support only conditional PC-relative branches. [2 pts]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts