Answered step by step

Verified Expert Solution

Question

1 Approved Answer

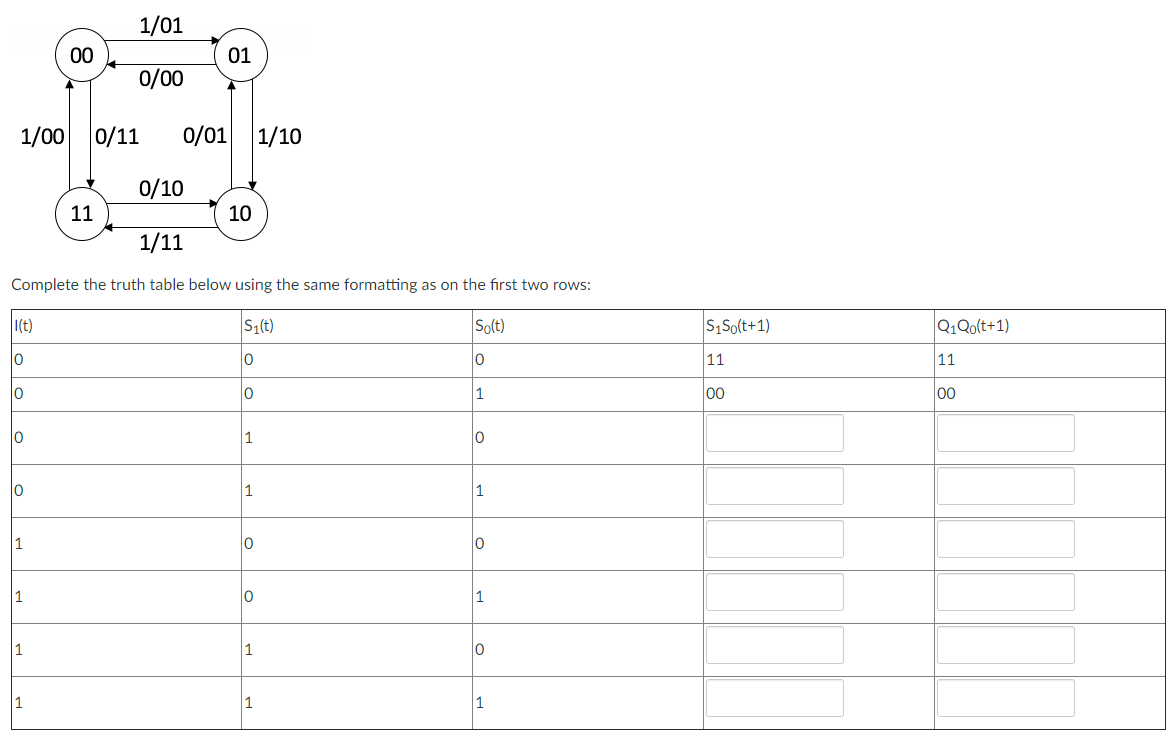

Consider a modulo 4 two-bit up-down counter with input I. I=1 causes the count to increment, e.g., 00->01->10->11, cycling back to 00 from state 11

Consider a modulo 4 two-bit up-down counter with input I. I=1 causes the count to increment, e.g., 00->01->10->11, cycling back to 00 from state 11 (in other words, counting from 0 up to 3 repeatedly). I=0 causes the count to decrement, e.g., 11->10->01->00, cycling back to 11 from state 00. The output values (Q1(t+1) and Q0(t+1)) will always be the same as the next state (S1(t+1) and S0(t+1)) for this device.

The state transition diagram for this device is shown below:

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started