Question

Consider a processor with multiple machine cycle control per instruction cycle. THE its architecture implements a stack architecture, but with some variations that will be

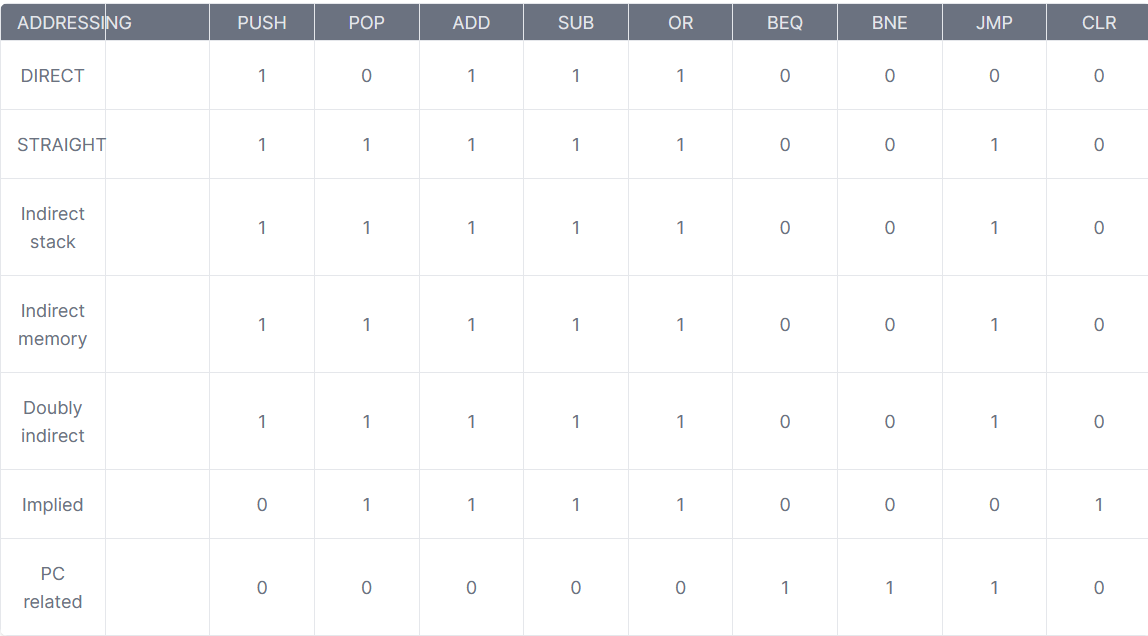

Consider a processor with multiple machine cycle control per instruction cycle. THE its architecture implements a stack architecture, but with some variations that will be described next. The MDR of this architecture includes, in addition to the stack, an ALM arithmetic/logic unit, a MEM memory unit, the PC program counter unit, as well as a number of special purpose registers, which serve to store information produced and consumed within the same instruction. The stack contains a word store and a pointer to its top, and it works based on four microfunctions activated by control signals of the same name: up, which raises the stack pointer by one position by inserting a data word; in the location it was previously pointing to, dn1, which depresses the stack pointer by one location, dn2, which depresses the stack pointer by two locations, and clr, which sets the stack pointer to its initial value. All changes to the stack state occur on falling clock pulse. The stack has two read ports, though A and B, and one write port, let S. Although writing to the stack is done only with the up signal, the read is done without a control signal and does not depress the stack pointer, while the two values read and sent to the read ports come from both positions immediately below the top of the stack. Suppose we want to support the following commands in our processor, with corresponding addressing:

where '1' means support, and '0' means no support of the command-addressing combination. More specifically: - The PUSH instruction inserts a word of data onto the stack, either from memory in a way that will be explained below, either from the command word with direct addressing and sign extension. The data is stored on the stack. - The commands ADD, SUB and OR perform an operation in ALM, with the first operand from port A of the stack, and the second operand either as a direct operand from the word instruction sign-extended for the first two instructions, either implicitly from port B of the stack, or from memory in a manner explained in and the result is stored on the stack. - The POP instruction pops a word of data off the stack. Implied addressing here it means that the data is simply removed and lost. In any other case, the data is sent to memory in a way that will be explained later. The data is taken from port A of the stack, except in the case of indirect addressing stack, so it is taken from port B of the stack. - The commands BEQ and BNE implement a branch in the code, after comparing the two words of data received from ports A and B of the stack, and on a true condition, with a jump to a PC-relative address. - The JMP command performs a jump in the code, to an address that is either given in a way that will explained below, whether it is PC related. - The CLR instruction resets the stack to its initial state, emptying any of its contents. Implicit addressing here means there is no finale.

In all instructions, whatever is read from the stack is removed from itEach instruction word contains, in addition to the function code and possible operands, 7 addressing digits, even D1 to D7, which indicate the addressing method of the command, in the order they are given in the table above. Specifically for memory addressing we have:

- In direct addressing the memory address is taken from the command word, or a combination of the end of the command word and the PC. - In indirect stack addressing the memory address is taken from the stack. In particular, in the PUSH and POP instructions the address is taken from port A of the stack, while in the ADD, SUB and OR instructions the address is taken from port B of the stack. - In indirect memory addressing the memory address is taken from the memory, from an address given directly by the command word, or a combination of the end of the command word and the PC. - Double indirect memory addressing is memory indirect in which the address is given by stack indirect addressing.

Each command activates a single addressing digit, which must match in a method accepted by the command. Also, whenever a memory address is taken directly from the instruction word, if the address space is not covered by the range of directly, the most significant digits of the address are taken from the PC.

A. Give the MDR diagram of the stack architecture to support the above commands. Add as many special purpose registers as you deem necessary so that achieve the fastest number of machine cycles for the supported instructions, don't but allowing sequentially dependent microfunctions to be executed in the same cycle machine. Define the MDR control signals you designed, which should include the stack control signals as defined above. Assume that if a stack overflow or underflow occurs, an appropriate exception is raised on the processor. Hint: Use the fact that stack state changes occur on the falling edge of the clock pulse.

B. Study the sequence of instruction phases, for each addressing method they support, and provide the architecture state diagram for implementation control hardwired logic. Reuse as many states as you can. Consider whether you can delegate some micro-functions to the decoding phase, and what they will be them to gain a machine cycle in executing some of its commands architecture.

C. Give the state transition conditions for the diagram you drew, as well as the logical expressions for the architecture control signals.

\begin{tabular}{|c|c|c|c|c|c|c|c|c|c|} \hline ADDRESSIN & PUSH & POP & ADD & SUB & OR & BEQ & BNE & JMP & CLR \\ \hline DIRECT & 1 & 0 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ \hline STRAIGHT & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ \hline \begin{tabular}{c} Indirect \\ stack \end{tabular} & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ \hline \begin{tabular}{l} Indirect \\ memory \end{tabular} & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ \hline \begin{tabular}{l} Doubly \\ indirect \end{tabular} & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ \hline Implied & 0 & 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ \hline \begin{tabular}{l} PC \\ related \end{tabular} & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 1 & 0 \\ \hline \end{tabular}Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started