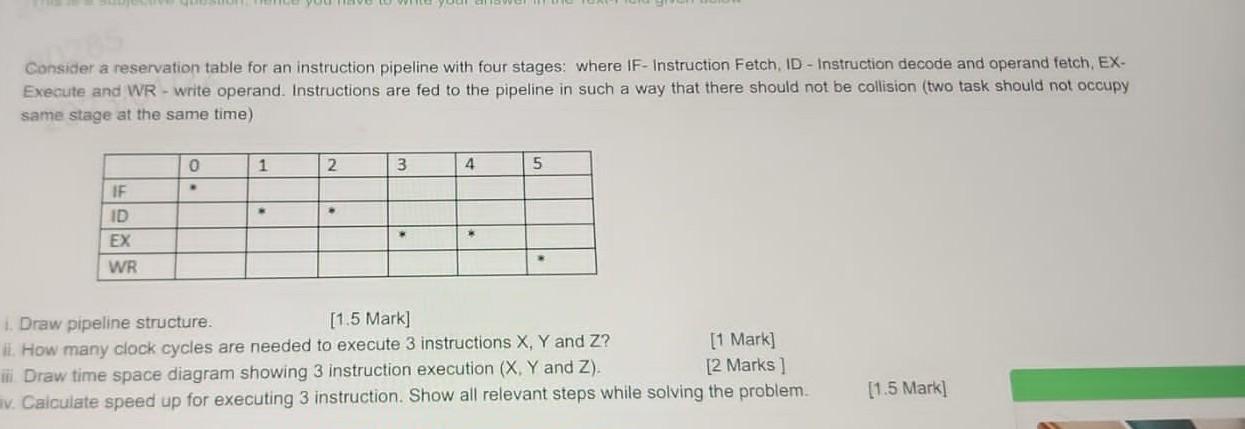

Question: Consider a reservation table for an instruction pipeline with four stages: where IF-Instruction Fetch, ID-Instruction decode and operand fetch, EXExecute and WR - write operand.

Consider a reservation table for an instruction pipeline with four stages: where IF-Instruction Fetch, ID-Instruction decode and operand fetch, EXExecute and WR - write operand. Instructions are fed to the pipeline in such a way that there should not be collision (two task should not occupy same stage at the same time) Draw pipeline structure. [1.5 Mark] How many clock cycles are needed to execute 3 instructions X,Y and Z? [1 Mark] Draw time space diagram showing 3 instruction execution (X,Y and Z ). [2 Marks] Calculate speed up for executing 3 instruction. Show all relevant steps while solving the problem. [1.5 Mark]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts