Question

Consider a single-issue design with a single execution pipeline with five-stages (Fetch, Decode, Execute, Memory, Write Back) capable of beginning execution of one instruction per

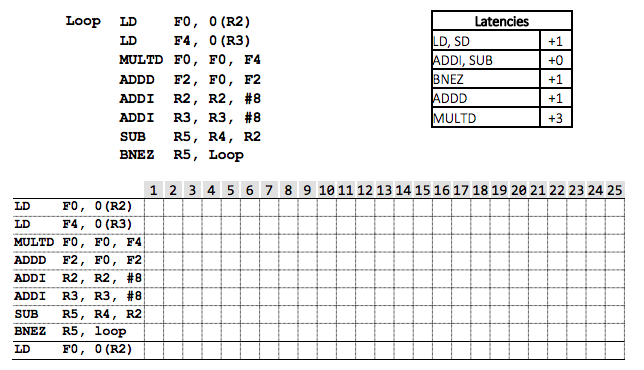

Consider a single-issue design with a single execution pipeline with five-stages (Fetch, Decode, Execute, Memory, Write Back) capable of beginning execution of one instruction per cycle with data forwarding and bypassing hardware, all memory accesses take 1 (one) clock cycle, and all memory references hit in the cache. Assume that the branch is handled by predicting it not taken. Use the following code fragment and assume that the initial value of R4 is R2+440. Please show the timing of the instruction sequence for this pipeline using the given pipeline chart. How many cycles does this loop take to execute?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started